Wright State University CORE Scholar

Browse all Theses and Dissertations

Theses and Dissertations

2020

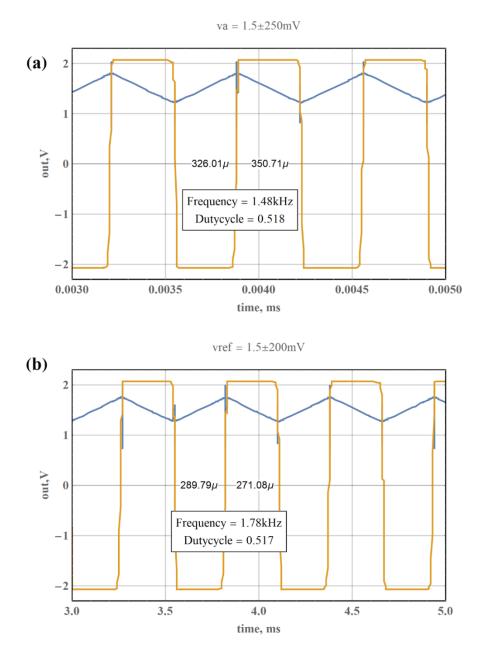

# Logistic Function based Nonlinear Modeling and Circuit Analysis of the Bipolar Vacancy Migration Memristor

Isaac P. Abraham Wright State University

Follow this and additional works at: https://corescholar.libraries.wright.edu/etd\_all

Part of the Electrical and Computer Engineering Commons

#### **Repository Citation**

Abraham, Isaac P., "Logistic Function based Nonlinear Modeling and Circuit Analysis of the Bipolar Vacancy Migration Memristor" (2020). *Browse all Theses and Dissertations*. 2302. https://corescholar.libraries.wright.edu/etd\_all/2302

This Dissertation is brought to you for free and open access by the Theses and Dissertations at CORE Scholar. It has been accepted for inclusion in Browse all Theses and Dissertations by an authorized administrator of CORE Scholar. For more information, please contact library-corescholar@wright.edu.

# LOGISTIC FUNCTION BASED NONLINEAR MODELING AND CIRCUIT ANALYSIS OF THE BIPOLAR VACANCY MIGRATION MEMRISTOR

A dissertation submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

by

#### ISAAC P. ABRAHAM

M.S.EG., Wright State University, USA, 1997

B. Tech., University of Kerala, India, 1993

2020

Wright State University

#### WRIGHT STATE UNIVERSITY GRADUATE SCHOOL

April 06, 2020

I HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER MY SUPERVISION BY <u>Isaac P. Abraham</u> ENTITLED <u>Logistic Function based Nonlinear</u> <u>Modeling and Circuit Analysis of the Bipolar Vacancy Migration Memristor</u> BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF <u>Doctor</u> <u>of Philosophy</u>.

> Saiyu Ren, Ph.D. Dissertation Director

Fred Garber, Ph.D. Interim Chair, Electrical Engineering

Barry Milligan, Ph.D. Interim Dean of the Graduate School

Committee on Final Examination:

Saiyu Ren, Ph.D.

Ray Siferd, Ph.D.

Marty Emmert, Ph.D.

Marian Kazimierczek, Ph.D.

Yan Zhuang, Ph.D.

#### ABSTRACT

Abraham, Isaac P., Ph.D., Electrical Engineering Ph.D. program, Wright State University, 2020. Logistic Function based Nonlinear Modeling and Circuit Analysis of the Bipolar Vacancy Migration Memristor.

Memristor is an acronym for **mem**ory **resistor**. Memristors promise to be building blocks for high density memory and analog computation. Hewlett Packard's announcement in 2008 of having fabricated a memristor on an integrated circuit scale has created a tangible excitement in this field. Understanding and exploiting the full potential of these devices requires good compact models. Symbolic modeling provides a balance between achieving accurate empirical fit and generating closed form expressions. This dissertation simplifies the transport equation into a variable coefficient advection equation, very similar to a Burgers' equation traditionally used in fluid dynamics. The Burgers'-like model reveals the dual variable resistance initially proposed by HP that has served as a gold standard to date. The Burgers' model also shows the emergence of an active phenomenon within the device as some researchers have suspected. Results from this model are compared favorably with independent experimental data. The insight obtained from this computational ion transport model is the motivation for proposing a simpler computational logistic function based memory resistance model. The logistic model is a solution to the well-known logistic equation and map. This relationship between functions and maps opens the door to understanding how the memristor can exhibit sensitivity to initial conditions as claimed by some researchers. The logistic model is validated by fitting to experimental data. The usability of the model in practical circuit design is demonstrated with a relaxation oscillator implemented in LTSpice. The oscillator implemented is power and reliability aware. A formal method to estimate the frequency of such a nonlinear circuit is presented. Computationally estimated frequency is validated against results from LTSpice. A variant of the oscillator is shown to function as a simple offset voltage detector. Unlike numerical methods, the symbolic, closed form approach in this dissertation provides an unparalleled perspective into the inner workings of the memristor. The peer reviewed, published findings of this research invalidate the claim that the memristor is a passive fundamental circuit element; an issue associated with the device since its inception.

# **Table of Contents**

| 1 Introduction                       |

|--------------------------------------|

| 1.1 Historical Hysteretic Devices    |

| 1.2 Contemporary Hysteretic Devices  |

| 1.2.1 Pre Hewlett-Packard            |

| 1.2.2 The Hewlett Packard Memristor  |

| 1.3 Structure and characteristic     |

| 1.3.1 Physical structure             |

| 1.3.2 Bipolar switching              |

| 1.3.3 Fingerprints of the Memristor7 |

| 1.4 Memristors and Computing         |

| 1.5 Survey of Models                 |

| 1.5.1 Discrete Time                  |

| 1.5.2 Continuous Time                |

| 1.6 Objectives of Dissertation       |

| 1.7 Organization of Dissertation     |

| 1.8 Chapter Summary                  |

| 2 | Cor | mpu | tational Ion Transport Model               | . 19 |

|---|-----|-----|--------------------------------------------|------|

|   | 2.1 | Me  | mristor Life Cycle                         | . 19 |

|   | 2.2 | Def | finitions                                  | 20   |

|   | 2.3 | Gov | verning Variable Coefficient Advection PDE | 21   |

|   | 2.3 | .1  | Model derivation                           | . 21 |

|   | 2.3 | .2  | Solution                                   | . 23 |

|   | 2.3 | .3  | Error term                                 | 24   |

|   | 2.3 | .4  | Solution verification                      | . 25 |

|   | 2.4 | Exp | pressions for Memristor Characteristics    | 26   |

|   | 2.4 | .1  | Computational framework                    | . 27 |

|   | 2.4 | .2  | Accumulation boundary                      | . 27 |

|   | 2.4 | .3  | Vacancy concentration                      | 29   |

|   | 2.4 | .4  | Resistance                                 | 29   |

|   | 2.4 | .5  | I-V curves                                 | . 31 |

|   | 2.4 | .6  | Switching time                             | . 33 |

|   | 2.4 | .7  | Switching energy                           | 36   |

|   | 2.4 | .8  | Shelf life                                 | 37   |

|   | 2.5 | Mo  | del Validation                             | 38   |

|   | 2.6 | Cha | apter Summary                              | . 39 |

| 3 | Co  | mpu | tational Logistic Model                    | . 40 |

|   | 3.1 | Background                                    | 40 |

|---|-----|-----------------------------------------------|----|

|   | 3.2 | Motivation                                    | 41 |

|   | 3.3 | The Logistic Function                         | 41 |

|   | 3.4 | The Logistic Equation                         | 43 |

|   | 3.5 | The Logistic Map                              | 44 |

|   | 3.6 | Relation to fluid dynamics                    | 46 |

|   | 3.7 | Origin of oscillatory response                | 48 |

|   | 3.8 | Chapter Summary                               | 48 |

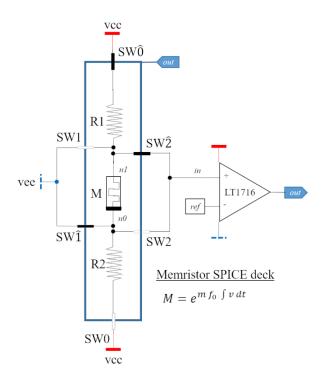

| 4 | SPI | CE Model                                      | 50 |

|   | 4.1 | Background                                    | 50 |

|   | 4.2 | Simplified Computational Ion Transport        | 51 |

|   | 4.3 | Structure of SPICE Model                      | 53 |

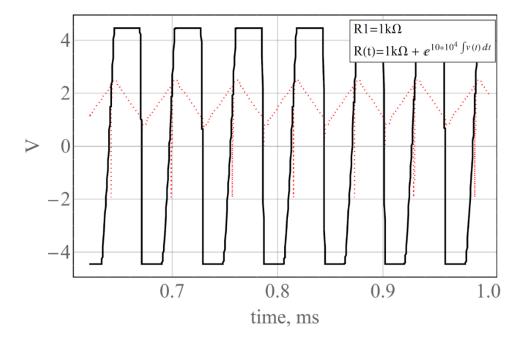

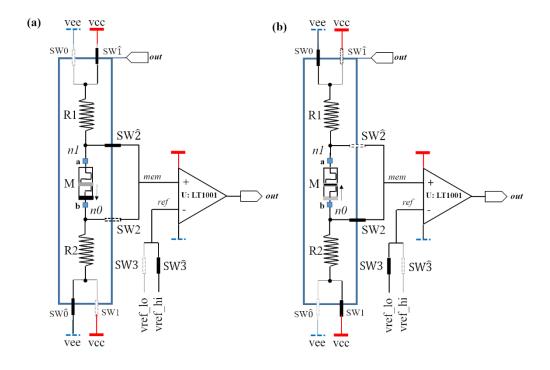

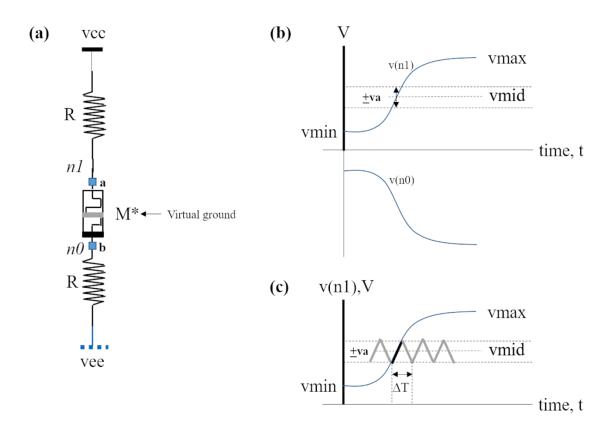

|   | 4.4 | Relaxation oscillators                        | 54 |

|   | 4.4 | .1 Background                                 | 54 |

|   | 4.4 | .2 Abel model-based relaxation oscillator     | 55 |

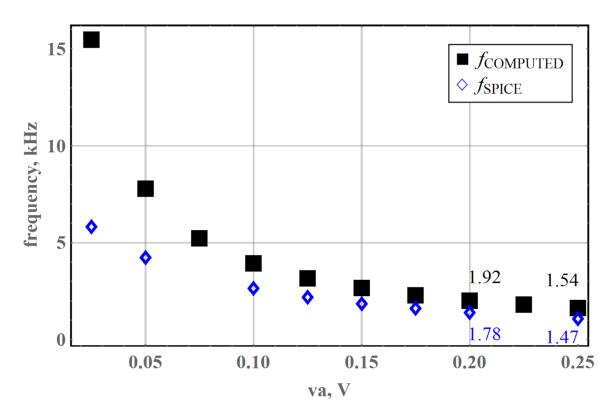

|   | 4.4 | .3 Logistic model-based relaxation oscillator | 61 |

|   | 4.5 | Scope of the logistic model                   | 69 |

|   | 4.5 | .1 I-V curves                                 | 69 |

|   | 4.5 | .2 Sensitivity to temperature                 | 71 |

|   | 4.5 | .3 Current mode operation                     | 72 |

|   | 4.5        | .4   | Integration with external nonlinear elements | 74 |

|---|------------|------|----------------------------------------------|----|

|   | 4.5        | .5   | Empirical modeling                           | 76 |

|   | 4.6        | Cha  | pter Summary                                 | 77 |

| 5 | Fui<br>5.1 |      | ental Issues                                 |    |

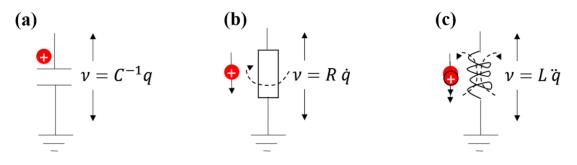

|   | 5.2        | Fun  | damental passives                            | 79 |

|   | 5.3        | Met  | thod to locating existing elements           | 79 |

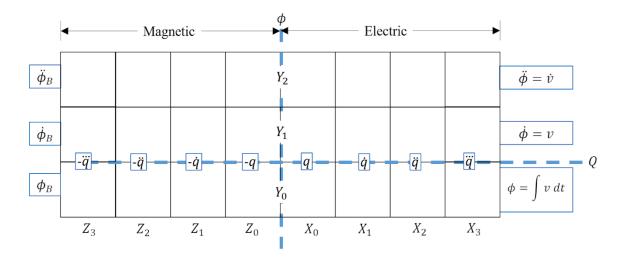

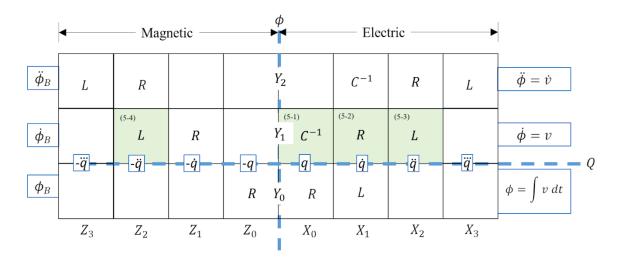

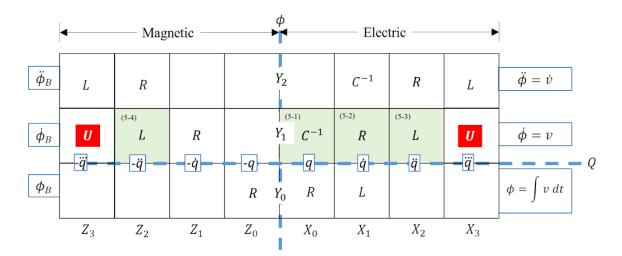

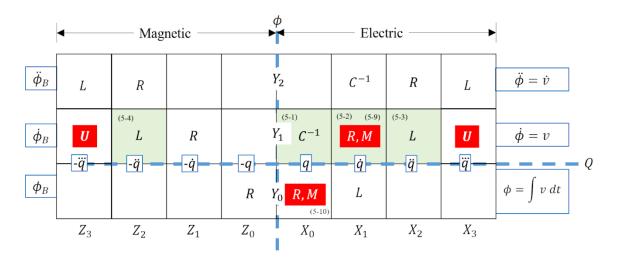

|   | 5.4        | Peri | odic table of fundamental devices            | 82 |

|   | 5.4        | .1   | Frame                                        | 83 |

|   | 5.4        | .2   | Axes                                         | 83 |

|   | 5.4        | .3   | Existing fundamental elements                | 84 |

|   | 5.4        | .4   | New fundamental elements                     | 85 |

|   | 5.4        | .5   | Memristor in the periodic table              | 87 |

|   | 5.5        | Ato  | micity and ion transport                     | 88 |

|   | 5.6        | Ado  | litional anomalies                           | 90 |

|   | 5.6        | .1   | The passive memristor model                  | 90 |

|   | 5.6        | .2   | The incomplete statement of fingerprint 1    | 91 |

|   | 5.6        | .3   | The trivially stated fingerprint 2           | 91 |

|   | 5.7        | Neg  | gative resistance explained                  | 93 |

|   | 5.8        | Wh   | at is the memristor?                         | 95 |

| 5 | 5.9 Cl | hapter Summary              | 96  |

|---|--------|-----------------------------|-----|

| 6 | Conclu | usion and Future Work       |     |

| e | 5.1 Co | onclusion                   | 97  |

|   | 6.1.1  | Computational Ion Transport | 97  |

|   | 6.1.2  | Logistic Model              |     |

|   | 6.1.3  | SPICE                       |     |

|   | 6.1.4  | Fundamental Issues          | 100 |

| 6 | 5.2 Fu | uture Work                  | 101 |

|   | 6.2.1  | Theoretical                 | 101 |

|   | 6.2.2  | SPICE                       | 101 |

| 7 | Refere | ences                       | 103 |

# List of Figures

| Fig. | 1.1 Memristive current-voltage curves over the centuries                              |

|------|---------------------------------------------------------------------------------------|

| Fig. | 1.2 Free ion migration determines device resistance                                   |

| Fig. | 1.3 The bipolar (a) I-V curve and (b) rheostat model [5]6                             |

| Fig. | 1.4 Vacancy migration and dual variable resistance                                    |

| Fig. | 1.5: HP model response                                                                |

| Fig. | 2.1 Memristor life cycle                                                              |

| Fig. | 2.2 Model of ion migration in the memristor                                           |

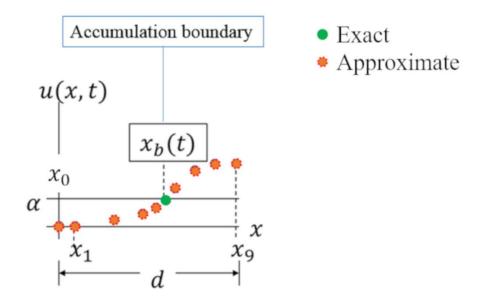

| Fig. | 2.3 Exact and approximate regions of vacancy evolution                                |

| Fig. | 2.4 Ion boundary evolution                                                            |

| Fig. | 2.5 Ion evolution along the normalized length of the memristor device                 |

| Fig. | 2.6 Device resistance as a function of time                                           |

| Fig. | 2.7 Simulated memristor I-V curves demonstrating the three fingerprints               |

| Fig. | 2.8 Model for estimating transition time                                              |

| Fig. | 2.9 Relationships between ion concentration, switching time and resistance ratio 36   |

| Fig. | 2.10 Ions dissipating during shelf time                                               |

| Fig. | 3.1: Transient resistance-time curves comparing computational ion transport, logistic |

| and  | simplified logistic models                                                            |

| Fig. | 3.2 Orbit plot for (3-9)                                                              |

| Fig. | 5.5 Memristor in the periodic table.                                           | . 87 |

|------|--------------------------------------------------------------------------------|------|

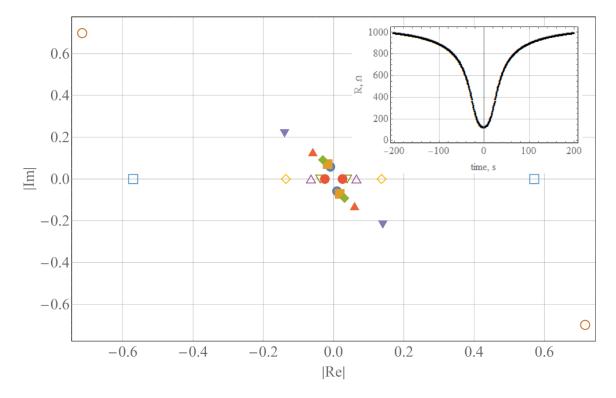

| Fig. | 5.6 Complex plane plot of DVR model                                            | . 89 |

| Fig. | 5.7 Memristor current- and voltage-time curves.                                | . 92 |

| Fig. | 5.8 (a) I-V curves over increasing frequencies and (b) lobe area vs. frequency | . 92 |

| Fig. | 5.9 Negative resistance explained by ion transport                             | .94  |

| Fig. | 5.10 Memristor composite                                                       | . 96 |

# List of Tables

| Table 2.1 Table of default parameter values.                               | 27 |

|----------------------------------------------------------------------------|----|

| Table 2.2 Validation of transition time against independent empirical data | 39 |

| Table 4.1 Table of component values for the Abel oscillator                | 59 |

| Table 4.2 Table of component values associated with Fig. 4.7               | 63 |

# Acknowledgements

I acknowledge the opportunity given to me by the Department of Electrical Engineering, College of Engineering and Computer Science, Wright State University, Dayton OH, to pursue this research. Thank you to my advisors Dr. S. Ren and Dr. R. E. Siferd for guidance with merging a theoretical research with practical application.

### **1** Introduction

A two terminal resistor that retains its prior programmed resistance is called a **mem**ory **resistor**. The phenomenon is called nonvolatile memory effect. In contemporary electrical phraseology, resistance R is a phenomenological constant, defined as the ratio of voltage to current. The phenomenological constant associated with memory resistance is memristance M, defined as the ratio of electric flux to charge. Memristance is characterized by hysteresis in the device output characteristic curve. Hysteresis causes a specific stimulus to have two different responses depending on the direction of travel of the stimulus. Memristive hysteresis appears in voltage-current coordinates, not in the coordinates of the memristor's constitutive relation which are flux and charge.

#### 1.1 Historical Hysteretic Devices

The modern memristor was postulated as a theoretical fundamental device by Leon Chua in 1971 [1]. However, the phenomenon of memristance has been observable in electrical experiments from approximately two hundred years ago. Prodromakis et al. survey a detailed collection of historical examples ranging from vacuum tubes, mercury vapor lamp, silver sulfide-based thermistors and the voltaic pile [2]. Fig. 1.1 shows a sample from Prodromakis' survey.

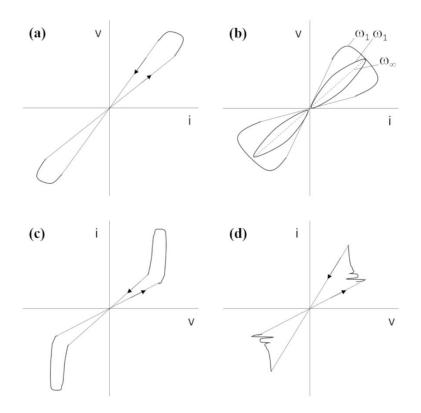

Fig. 1.1 Memristive current-voltage curves over the centuries.

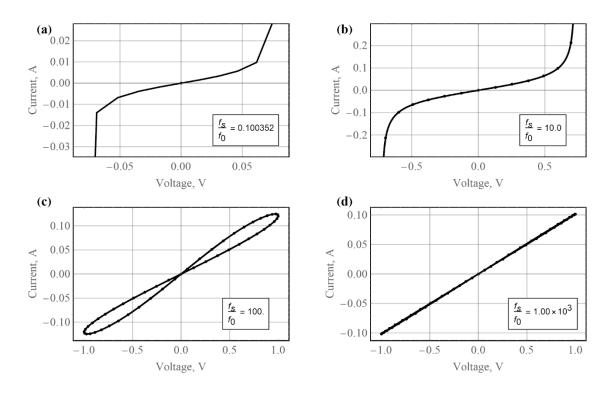

Fig. 1.1 shows a variety of bipolar current-voltage (I-V) response curves transcribed from historical literature into the review in [2] and other referenced documents. Panel (a) shows a tungsten filament I-V curve as reproduced in [2] from the original textbook "Fundamentals of Discharge Tube Circuits" by V. J. Francis. Panel (b) shows Chua's conceptual I-V curves with frequency dependence as mentioned in [3]. Panel (c) is Argall's experimental titanium oxide I-V curves from [4] and panel (d) shows Williams et al. demonstrating simulated and experimental I-V curves in [5].

If a pinched hysteresis curve is the signature of memristance, then it is also observable in natural phenomena. The analemma curve which plots the year-round position of the sun from a fixed geographical location and time looks very much like the bow-tie or pinched hysteresis curves described above [6]. For a memristor this signature bowtie or pinched hysteresis I-V curve is generated with a sinusoidal input applied to the two terminal memristor device.

#### 1.2 Contemporary Hysteretic Devices

#### 1.2.1 Pre Hewlett-Packard

A more modern and often referenced experimental work that reveals memristive characteristics in thin films is Argall [4]. Argall's paper shows bowtie I-V curves generated with anodized titanium dioxide film and copper electrodes. Switching is induced by voltage cycling. Within three years in 1971 Chua published the theoretical framework to the memristor, proposed a device symbol and set forth the basic abstract equations that should describe any memristive device [1]. Chua and Kang later generalized the notion of memristance to memristive systems [7]. The common, recurring idea among all memristive systems is that the hysteretic effect of the memristive system decreases as the frequency increases and hence it eventually degenerates into a purely resistive system without memory.

#### 1.2.2 The Hewlett Packard Memristor

The lull in memristor research since 1971 ended when researchers at Hewlett Packard (HP) announced finding the missing memristor in their seminal paper [5]. The paper expounds on experimental results from using a titanium dioxide thin film. The titanium dioxide in proximity to the contacts was found to split into two layers, namely an oxygen deficient layer of TiO<sub>2-x</sub> and stable TiO<sub>2</sub>. The oxygen deficient titanium dioxide layer functions as a donor of electrons while the positive oxygen ions (O<sup>2+</sup>) are the mobile vacancies. The associated I-V curves exhibit hysteresis along with bipolar switching. Bipolar switching

requires voltage reversal to return the device to a prior state. The authors propose an ohmic electronic conduction model where linear ionic drift in a uniform field controls the device resistance. This first abstract circuit model has series dual variable resistors as sketched in Fig. 1.3 (b). In late 2008, Williams writes in the IEEE Spectrum detailing the experimental search for the (till then) "mythical" memristor [3]. The article in Spectrum visualizes memristors in the role of nonvolatile memory elements and two-state field programmable gate arrays with reduced area and lower power.

#### 1.3 Structure and characteristic

#### 1.3.1 Physical structure

The memristor has a metal-insulator-metal (MIM) structure [3], [8]. The metal end plates form the device terminals. The end plates at each end can be made of different materials and dimensions. The plates serve as the boundary to the "insulating" sandwich. The "insulator" is the chemical that contains the mobile vacancies. The word insulator is used only to help compare the memristor to a MIM structure. The chemical species between the plates conducts electronic current. Titanium dioxide [9], copper oxide [10], nickel oxide [11] etc. are used to form this chemical sandwich. Experimentalists work with end plates of various sizes to investigate the impact of area, surface roughness etc. on the memristor characteristic. The thickness of the sandwich is yet another variable that has a large range. Memristors in literature can range from 500nm [12] down to about 50nm [3] or even 30nm [13]. The theoretical limits might be around 10nm according to Strukov [5]. Fig. 1.2 shows a cartoon of the ion migration under the action of an applied external voltage.

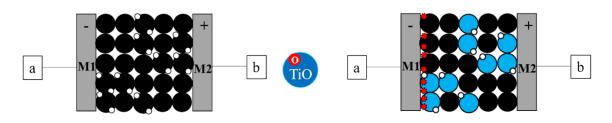

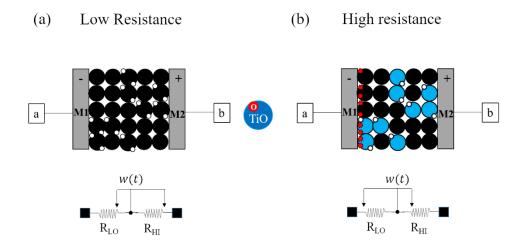

(b) High resistance

Fig. 1.2 Free ion migration determines device resistance.

In Fig. 1.2 (a), the device is in low resistance. The metal end plates are marked M1 and M2 and associated with device terminals a and b respectively. The large black circles are the neutral  $TiO_2$ ; where the oxygen atoms are shown as white circles hugging the outline of the black circles. From experiments it is known that only a small fraction of TiO2 can generate free oxygen ions. Hence Fig. 1.2 (a) shows only some of the TiO2 with their oxygen bonds – ready to break free.

In Fig. 1.2 (b) a voltage is applied between the pins a and b. From each of the previously identified TiO2 locations, one positively charged oxygen ion breaks away. This leaves behind a blue-colored negatively charged but immobile TiO. The attached oxygen is shown as a white circle. The mobile positive oxygen ions are shown with a dotted red circle. These ions have drifted to the negative plate of the device. Strukov identifies the oxygen as positively charged [3]. This is also easily verified with an electron shell diagram. Electrons attempting to transit the chemical species now face a large negative field of TiO. The distribution profile of the positive and negative ions determines the device resistance.

#### 1.3.2 Bipolar switching

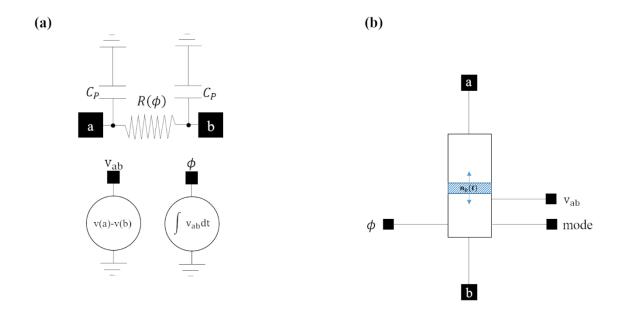

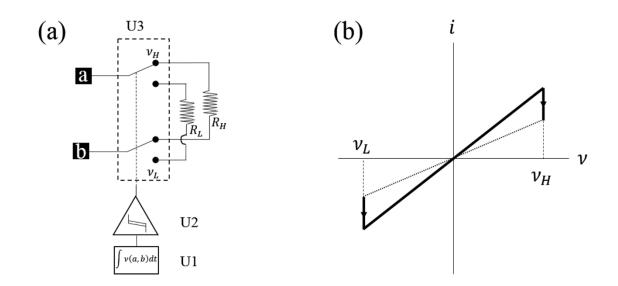

Bipolar implies the need for a positive and negative voltage across the memristor to program and reset the device. Fig. 1.3 shows the I-V and circuit model.

**Bipolar I-V Curve**

**Bipolar Circuit Model**

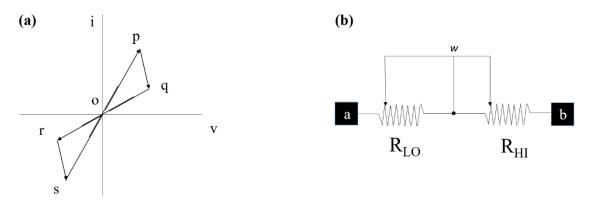

Fig. 1.3 The bipolar (a) I-V curve and (b) rheostat model [5].

Fig. 1.3 (a) shows the I-V curve of the bipolar memristor. When the input voltage is zero, response current is also zero; suggesting that there is no permanent energy storage or generator element within. Assuming the device was parked in the low resistance state, the curve traces **o-p** where it switches to the high resistance state along **p-q**, with lower current. When the stimulus voltage is reduced, the current traces back to the origin along **q-o**. If the voltage were to increase without an excursion to the negative voltage, the current will be low and trace back and forth along **o-q**. The device will never exit the high resistance state if the polarity of the voltage does not reverse. When the applied voltage traverses to the negative, the current will trace **o-r** and eventually switch to the low resistance state along **r-s**. When the voltage increases to zero and crosses over to positive, the locus traces **s-o-p**.

In short, a bipolar memristor can only switch states while transiting the origin, into quadrants one or three.

The popular and accepted model for the memristor was proposed by HP's Strukov and Williams. A sketch is shown in Fig. 1.3 (b). The discussion associates  $(R_{LO}, R_{HI})$  with  $(R_{ON}, R_{OFF})$ . The input and output pins are labeled **a** and **b**. The two terminal model has two resistors  $R_{ON}$  and  $R_{OFF}$  with a short-circuiting slider in between. The slider can short circuit  $R_{ON}$ ,  $R_{OFF}$  or parts of both emulating resistance switching between the low  $R_{ON}$  and high  $R_{OFF}$ . The variable *w* associated with the slider indicates the time dependent state variable that stores information about the positioning of the slider, which in turn determines the device resistance.

#### 1.3.3 Fingerprints of the Memristor

Adhikari and Chua have codified a set of three simple qualities to identify memristive behavior [14]. The sketched Fig. 1.2 (b) exhibits all the three fingerprints stated below.

#### 1.3.3.1 Fingerprint 1: Pinched hysteresis loop

A pinched hysteresis loop is defined as one that passes through the point (v, i) = (0, 0). The pinched at the origin phenomenon is universal to all memristors independent of the stimulus applied to the device. This definition requires that the device cannot store energy. All the plots in Fig. 1.1 exhibit pinched hysteresis.

#### 1.3.3.2 Fingerprint 2: Hysteresis loop area is inversely proportional to frequency

A memristor will exhibit shrinking lobe area as the frequency of excitation increases. The reason for this is that with increasing excitation frequencies, the mobile ions do not depart from their initial positions farther enough to enter a higher or lower resistance state. Fig. 1.1 (b) shows the lobe area shrinking with increasing excitation frequency.

# 1.3.3.3 Fingerprint 3: Pinched hysteresis loop shrinks to a single valued function at infinite frequency Fingerprint 3 is a follow-on to fingerprint 2. When the excitation frequency is very high, the I-V curve resembles a line without any lobe. This line may be linear or nonlinear. Fig. 1.1 (b) shows the case where the collapsed lobe is linear.

#### 1.4 Memristors and Computing

Memristors are potential candidates to implement high density, low power and nonvolatile memory elements. In memory circuits, a logic "1" or "0" can be stored as a high or low resistance. Some research is focused on crossbar structures composed of hybrid CMOS/memristor circuits; although most studies generally focus on single memristors. This is starting to change with more researchers experimenting with their own choice of differently sized end plates and sandwich materials integrated into arrays.

Logic applications are an area of interest for researchers. Field Programmable Gate Array (FPGA) circuits may benefit from storing the microprocessor circuit configuration before powering down or to assist recovery, in a smaller and lower power memristor array rather than a traditional flash memory or static random access memory (RAM) [15]. Batas and Fiedler present a digital AND circuit using only memristors [16].

The use of hysteretic devices for analog computing can be traced to the 1960s. Memristors can implement the resistance switching component in mixed signal computing [15] and artificial neural networks [17]. Arithmetic operations can also be performed with device conductance representing the quantities being operated upon [18], [19]. An appropriately mature device model is desirable to support circuit design for such applications.

#### 1.5 Survey of Models

An understanding of the current state of memristor modeling is essential for placing this dissertation's symbolic model in context. Modeling can be broadly classified as discrete and continuous time. Each of these major categories may have uniquely distinguishable methods as sub categories.

#### 1.5.1 Discrete Time

#### 1.5.1.1 Piecewise

An early piece wise linear (PWL) model proposes to define the important segments of the Lissajous figure (or the bowtie curve) as straight lines. The result is an ideal bowtie [20]. Itoh and Chua present chaotic circuits based on PWL models in [21]. The main topic in that paper is bifurcation and chaos rather than the modeling aspect itself. Nevertheless, it develops on PWL modeling that Chua originally proposed in [1]. PWL models are not very interesting in themselves. However, they are easy to use, very suitable for modeling two-state circuit behavior and have low computational complexity.

#### 1.5.1.2 Numerical

Traditional numerical models rely on solving a problem by discretizing fundamental equations and solving them based on initial and boundary conditions. Most real-life problems are only tractable in this way. Numerical solutions however do not provide a closed form solution to readily reveal the characteristics of the device. Closed form or symbolic solutions are computable expressions. A thorough numerical study on memristive phenomenon is presented by Nardi et al. in [22] and [23]. Part I [22] presents the empirical data collected by the authors. Part II [23] creates a numerical model that is used to fit the experimental data. The drift-diffusion equation, Arrhenius law, Einstein relation and the

steady state Fourier equation are solved self-consistently using numerical methods, leading to dopant density, temperature and potential maps. The authors show relatively good agreement between modeling and the experiments. Each numerical simulation is just that one simulation. The user will have no idea about how a device state will evolve under different input conditions, unless a suite of simulations is performed under varying conditions.

#### 1.5.2 Continuous Time

Continuously differentiable ordinary differential equations (ODE) are also used for memristor modeling. Many ODE models can only be solved numerically even if their governing equations are specified in continuous time. Inclusion in this section does not imply that a closed form solution exists.

#### 1.5.2.1 The HP model

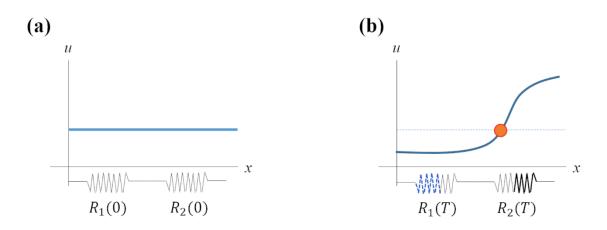

This commonly referenced memristor model is the dual variable resistor (DVR) model from HP [5]. It has closed form solutions. Their model consists of two series connected resistors and a slider that short circuits portions of the two resistors. Fig. 1.4 relates vacancy migration to resistance. The black circles are stable TiO2. The blue circles depict negatively charged, immobile TiO. Positively charged oxygen vacancies are depicted in red dots.

Fig. 1.4 Vacancy migration and dual variable resistance.

Fig. 1.4 (a) shows a cartoon of the vacancy distribution in the top panel along with the low resistance state of the device in the lower circuit diagram. In Fig. 1.4 (b), the vacancies have migrated to one end of the device and the associated circuit diagram shows the rheostat in its high resistance state. The DVR is an improvised circuit abstraction and does not reveal any specifics about vacancy dynamics. The presence of these two resistances cannot be inferred from the solution to HP's governing equations [5]. Equation (1-1) is an algebraic relation and it cannot be solved without the simple ODE in (1-2).

$$v(t) = \left(R_{ON} \frac{w(t)}{d} + R_{OFF} \left(1 - \frac{w(t)}{d}\right)\right) i(t)$$

<sup>(1-1)</sup>

$$\frac{dw(t)}{dt} = \mu_V \frac{R_{ON}}{d} i(t)$$

<sup>(1-2)</sup>

In (1-1) and (1-2),

v(t) is the time dependent voltage across the device,

$R_{ON}$  and  $R_{OFF}$  are the low and high resistance,

w(t) is the time-dependent position of the slider representing the boundary between the ion-rich and ion-poor regions of the device,

*d* is device length,

i(t) is the time-dependent current in the device and

$\mu_V$  is the mobility of the vacancies or ions.

The original HP model (1-2) assumes a linear movement of the rigid boundary between device regions that have different vacancy concentrations. Integrating (1-2) with respect to (w.r.t) time t results in w(t) in terms of charge q(t).

$$w(t) = \mu_V \frac{R_{ON}}{d} q(t)$$

<sup>(1-3)</sup>

Inserting (1-3) into (1-1) results in the equation for memristance. Assuming  $R_{ON} \ll R_{OFF}$ , equation (1-1) simplifies as follows.

$$M(q) = R_{OFF} \left( 1 - \mu_V \frac{R_{ON}}{d^2} q(t) \right)$$

<sup>(1-4)</sup>

Equation (1-4) is used by many authors to show memristive characteristics. It is a simplification that presents memristance as a function of charge which is in turn a function of time. The presence of time varying charge in (1-4) makes it inconvenient for manipulation in circuit design. Therefore, a solution relating memristance to voltage as a forcing function is desired.

Writing  $q(t) = \int i(t) dt$ , (1-4) becomes  $M(t) = R_{OFF} \left(1 - \mu_V \frac{R_{ON}}{d^2} \int i(t) dt\right)$ . Differentiating each side w.r.t time,

$$\frac{dM(t)}{dt} = -\frac{\mu_V R_{ON} R_{OFF}}{d^2} i(t) = -\frac{\mu_V R_{ON} R_{OFF}}{d^2} \frac{v(t)}{M(t)}.$$

(1-5)

This is equivalent to a first order nonlinear ODE of the form y y' = -k f; where y is the desired solution, f is the stimulus, both are functions of time and k is a constant [24].

Fig. 1.5: HP model response.

For  $v(t) = \sin(\omega t)$ , the solution to (1-5) is

$$M(t) = \pm \sqrt{\frac{M(0)^2 \,\omega + 2 \,k \cos(\omega \,t) - 2 \,k}{\omega}}.$$

(1-6)

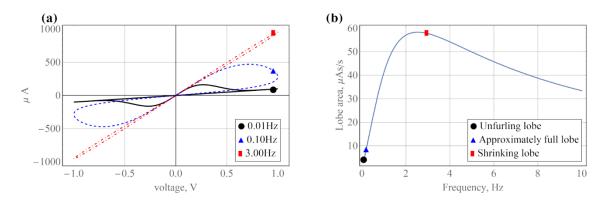

In (1-6), M(0) is known from design or calibration of a product and  $k = \frac{\mu_V R_{ON} R_{OFF}}{d^2}$ . Consider the response from the HP model using (1-6) as shown in Fig. 1.5. The plots were generated using an arbitrary  $\mu_V = 10^{-14} \frac{m^2}{V s}$ ,  $R_{ON} = 10\Omega$ ,  $R_{OFF} = 1 k\Omega$ , d = 32 nm and a forcing function  $v(t) = \sin(\omega t)$ . Under these conditions the natural frequency of the device is estimated to be  $f_0 = \frac{\mu}{d^2} = 9.77 Hz$ . Each panel of Fig. 1.5 is generated at a fraction  $\frac{f_s}{f_0}$  of the device natural frequency; where  $f_s$  is the stimulus frequency. Fig. 1.5 (a) shows that when the stimulus frequency is smaller than the natural frequency, the I-V lobe is incorrectly collapsed. There is no significant change in Fig. 1.5 (b) when the stimulus is an order of magnitude larger. Fig. 1.5 (c) shows that the lobe size has incorrectly increased when the stimulus is 100-times the device natural frequency. It is impossible for the lobe to appear as stimulus frequency increases; this contradicts fingerprint 2. In Fig. 1.5 (d) at 1000-times the device's natural frequency, the I-V curve has correctly collapsed to a straight line. In addition to these mixed correct and incorrect responses, the device model transitions from a collapsed nonlinear resistor at very low frequencies to a collapsed linear resistor at very high frequencies. This transition from linear to nonlinear is unexpected and incorrect.

Meuffels and Soni [25] present a strong case for why the modeling in [5] is insufficient in describing a real system. The authors point out that the notion of a rigid boundary between two regions with sparse and dense vacancies is conceptually weak. They also object to the idea of a linearly moving boundary, although Williams and Strukov circumvent the non-ideality by subsequently employing window functions to modify the movement of the boundary toward the device ends.

Window functions are arbitrary polynomials that modulate the equation for accumulation boundary movement, such that the boundary slows down and asymptotically approaches the end plates of the memristor. Window functions come in many forms. The expression  $f(w) = w(1-w)/d^2$  [5] is HP's version of a windowing function. Here variable w is a function of time as in w(t). Joglekar et al. propose  $f(w) = 1 - (2w - 1)^{2p}$ ,  $p \ge 1$  [26]. Biolek uses  $f(x) = 1 - (x - \operatorname{stp}(-i))^{2p}$ ,  $p \ge 1$  with a step defined as  $\operatorname{stp}(i) = \begin{cases} 1, i \ge 0 \\ 0, i < 0 \end{cases}$  [27]. Corinto et al. discuss a Boundary Condition Model (BCM) that uses HP's basic model, modulated by a variety of window functions [28]. The resulting model almost always can only be solved with numerical methods.

Publications [28], [29] and [30] that promise a symbolic approach invariably uses HP's basic equation paired with HP's-own window functions or that of Joglekar; providing no originality and are solved numerically. Without the manual insertion of nonlinearity, the raw HP model exhibits inconsistent behaviors presented in Fig. 1.5.

Nonetheless equations (1-1) and (1-2) satisfy Chua's definitions for a general memristive system and the ideal generic memristor. The generalized equations are shown below in (1-7) and (1-8) [5].

$$v(t) = R(w(t), i) i \tag{1-7}$$

$$\frac{dw(t)}{dt} = f(w(t), i)$$

<sup>(1-8)</sup>

#### 1.5.2.2 The shockwave model

The shockwave model approaches modeling with a generalization of the Burgers' equation [31]. In (1-9), u is mobile ion concentration, D is diffusion coefficient and f(u) is the concentration wave velocity as a function of ion concentration.

$$\partial_t u + f(u) \,\partial_x u = D \,\partial_{xx} u \tag{1-9}$$

Important assumptions in (1-9) are that nonlinear drift dominates diffusion, transverse currents are neglected and local resistance is a function of vacancy concentration. The ideas presented by Tang et al. result in a sharp and discontinuous shock wave front. However, this is at variance with the smoother sigmoid type vacancy evolution that Waser has presented in his surveys [12]. Similarly a discontinuous front is the very objection raised

by Meuffels and Soni. This shockwave model therefore serves to demonstrate that even among symbolic methods that seem similar there can be differences in how vacancy profile evolves; yet all of them exhibiting memristive qualities. Tang et al. observe the quadratic dependence of switching speed to device length and the existence of two distinct temporal phases during switching.

#### 1.6 Objectives of Dissertation

The objectives of this dissertation are as follows.

- Develop a simplified transport-based differential equation and symbolic solution. The simplified governing differential equation is the variable coefficient advection (VCA) equation. The VCA, its solution and inferences will be referred to as the computational ion transport model.

- Validate the computational model against independent experimental data. The computational model is further simplified to a form suitable for implementation in the Simulation Program with Integrated Circuit Emphasis (SPICE) and used in circuit simulations.

- Associate the computational ion transport compact model with a computational logistic differential equation (LDE). The LDE and its solution will be referred to as the logistic model. The LDE will be implemented in SPICE and used in circuit simulations.

• Use the computational and logistic models to tackle fundamental issues with the definition of the memristor. This dissertation examines if the memristor can be a fundamental passive circuit element.

The units in this dissertation adhere to the SI units [32].

#### 1.7 Organization of Dissertation

The dissertation is organized as follows.

- Chapter 1 is this chapter which serves as an introduction to the topic of memristors. It contains a survey of contemporary models. This sets the background for the state of the art in the field and places this dissertation in context. Chapter 1 also details the objectives and organization of this dissertation.

- Chapter 2 presents the derivation that transforms the basic transport equation into a variable coefficient equation and presents a symbolic solution. The computational model is used to derive a variety of expressions that demonstrate memristive characteristics. The output of the model is compared against empirical results from independent researchers.

- Chapter 3 associates the computational ion transport model with the computational logistic equation. Memristive characteristics are demonstrated with the logistic model.

- Chapter 4 demonstrates SPICE circuit simulations using the computational and logistic model. A relaxation oscillator that is unique to this dissertation is presented.

Simulations that explore the scope and versatility of the logistic model are presented and discussed.

- Chapter 5 is a review of fundamental findings from this research. This chapter reviews the memristor in the context of the three existing fundamental passive elements namely the resistor, capacitor and inductor. Our findings are demonstrated to be comparable with that of independent researchers. Significant findings that are divergent from the view of some researchers in the memristor community are explained clearly. Such findings are also published in high quality journals.

- Chapter 6 concludes this dissertation and suggests future work.

#### 1.8 Chapter Summary

The memristor is not an invention [2]. It belongs in the class of devices that exhibit a transient lag between applied stimulus and response or cause and effect. The contribution by the researchers at HP is the repeatable rendering of the phenomenon at the nanometer scale. Memristors may find application in implementing binary memory, logic and analog functions. Each application area is nascent and holds potential for discovery and innovation. The progress in each field however will depend on the availability of satisfactory models that can used with the tool suites appropriate for each field. Memristor device modeling is mostly incremental fine-tuning of the HP model with few other original approaches. This dissertation models the memristor with a single governing PDE. The results are abstracted to a logistic functional form. Memristor based computing is explored mathematically and in SPICE, using both the VCA model, its derived simplifications and the logistic model.

## **2** Computational Ion Transport Model

This chapter presents a simplification to the transport partial differential equation (PDE), resulting in the VCA PDE and a symbolic solution. The solution is validated by back-substitution into the PDE. The discussion in this chapter is substantially drawn from [33] and [34], where we first reported the development and evaluation of this technique.

#### 2.1 Memristor Life Cycle

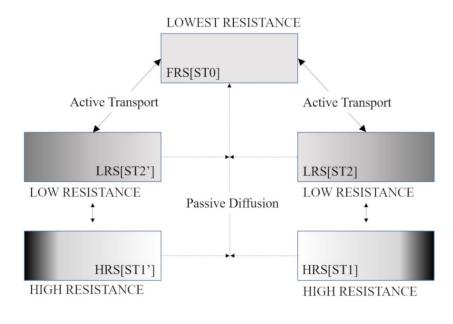

Prior to deriving a computational transport model, Fig. 2.1 shows a proposed memristor life cycle. This is the framework for understanding the main ion evolution mechanisms considered in this dissertation.

Consider a device in its fresh and lowest resistance state FRS (ST0). The application of a programming voltage causes the vacancies to migrate either left or right. This results in mirror symmetric states ST[1, 2] and ST[1', 2']. The highest possible resistance along either path is ST1 (or ST1'). State ST2 (or ST2') is some intermediate low resistance state. The mechanism that motivates programming is active transport in the presence of an electric field.

When a programmed device is left on the shelf for an extended time period, the ions naturally diffuse throughout the volume of the device. This passive diffusion is shown in dotted lines. Passive diffusion occurs from regions of high ion concentration toward regions of low ion concentration without any external voltage.

#### 2.2 Definitions

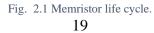

Consider a one-dimensional model of an ideal memristor to be a MIM sandwich with thickness d m. Let the ion concentration at any point within the sandwich be represented by u m<sup>-3</sup>. This is visualized in Fig. 2.2 which can locate an arbitrary distance along the device length on the x-axis and space time dependent ion concentration along the y-axis.

Fig. 2.2 Model of ion migration in the memristor.

Fig. 2.2 (a) shows the device in its low resistance state and has an equal concentration  $\alpha$  at all positions. Fig. 2.2 (b) shows the same device after the ions have evolved in the presence of an applied voltage. This evolution profile is qualitatively consistent with the expectation from Williams [3], Waser [12] and Tang [31] among others. The new feature in Fig. 2.2 (b) is the labeled location  $x_b(t)$ . This is the boundary that separates the ionrich from the ion-poor region of the memristor; alternatively referred to as w in Williams and Strukov's works. Fig. 2.2 (b) shows that this point always has a concentration equal to the initial distribution  $\alpha$ . An expression is later derived to compute the location of  $x_b(t)$ . To account for ion migration, let the mobility of the positively charged ions be uniform within this cross-section and represented by  $\mu$  m<sup>2</sup>s<sup>-1</sup>/V. Ion velocity in the presence of a voltage *V* will be represented by the Greek character upsilon, v m/s. The derivation of the simplified VCA PDE follows.

The key assumptions in the derivation are,

- vacancy and electric field are uniform within the device and

- vacancies do not exit the device boundaries.

#### 2.3 Governing Variable Coefficient Advection PDE

2.3.1 Model derivation

Consider the basic transport equation which models the movement of particles under the action of an applied stimulus.

$$u_t + (v \, u)_x = 0 \tag{2-1}$$

In (2-1) all variables are functions of (x, t). Subscripting indicates taking the derivative w.r.t the specified subscript. From Fig. 2.2 it is observed that the concentration u depends on the distance of a location x from the accumulation boundary  $x_b(t)$ . Therefore, apply the transformation  $u(x,t) \rightarrow u(x - x_b(t))$  and  $v \rightarrow v(x - x_b(t))$  and operate.

$$\left(\frac{\partial}{\partial t} + \frac{\partial}{\partial x}v(x - x_b(t))\right)u(x - x_b(t)) = 0$$

<sup>(2-2)</sup>

$$\frac{\partial}{\partial t}u - x'_b(t)\frac{\partial}{\partial x}u + v\frac{\partial}{\partial x}u + u\frac{\partial}{\partial x}v = 0$$

<sup>(2-3)</sup>

$$u_t + (v - x_b'(t))u_x + u v_x = 0$$

(2-4)

$$u_t + \vartheta \, u_x + u \, v_x = 0 \tag{2-5}$$

The velocity of the traveling point with constant concentration is termed the characteristic velocity [35]. Applying the transformation  $(v - x'_b(t)) \rightarrow \vartheta$ ,

$$u_t + \vartheta \, u_x + u \left( \vartheta + x'_b(t) \right)_x = 0. \tag{2-6}$$

$$u_t + \vartheta \, u_x + u \, \vartheta_x + u \, x_b'(t)_x = 0 \tag{2-7}$$

Since  $x_b(t)$  is a function only of time,  $x'_b(t)_x$  must equal zero. The fourth term of (2-7) is eliminated.

$$u_t + \vartheta \, u_x + u \, \vartheta_x = 0 \tag{2-8}$$

Equation (2-8) has two unknowns u and  $\vartheta$ . One of the unknowns must be known to find the other. If the third term is retained, there is no symbolic solution. Assume for the moment that  $u \vartheta_x$  is insignificant compared to the first and second terms giving the simplified PDE.

$$u_t + \vartheta \, u_x = 0 \tag{2-9}$$

The experimental and theoretical work of Williams [5], Waser [12], Larentis [23], Biolek [30] and Tang [31] suggest that a sigmoidal function can satisfy the ion evolution profile.

#### 2.3.2 Solution

In order to develop intuition about the structure of the solution, consider the sample equation  $u_t + \vartheta u_x = 0$  with  $\vartheta = (x/t)$ . One solution among many others is  $u(x,t) = 1/(1 + e^{-x/t})$ . This form is chosen for its ability to demonstrate a sigmoidal temporal ion evolution. Since it resembles a Heaviside step function [36], the mobility  $\mu$  and electric field *E* are used to modulate the slope of the sigmoid. The  $(x - x_b(t))$  term models the movement of the ion boundary. The structure of the solution was inferred from the representation of the Heaviside step [36] and the sigmoid function [37].

$$u(x,t) = \frac{1}{1 + a \, e^{-\frac{1}{d}\mu E \left(\frac{x - x_b(t)}{d}\right)t}}$$

(2-10)

In (2-10),

*a* is a constant that can be evaluated from initial conditions,

*d* is the device length,

$\mu$  is ion or vacancy mobility in  $m^2 v^{-1} s^{-1}$ ,

E is the electric field within the device, defined as voltage per unit device length v/d,

x is any location within the device,

$x_b(t)$  is the moving ion boundary and

t is time.

Defining electric flux  $\phi = \int_{t=0}^{T} v(t)dt$ , the solution can be expression in its normalized form where concentration is  $0 \le u \le 1$  and  $0 \le n \le 1$  with  $n = \frac{x}{d}$ , the normalized distance.

$$u(n,t) = \frac{1}{1 + a \, e^{-f_0 \, \phi \, (n - n_b(t))}} \tag{2-11}$$

#### 2.3.3 Error term

From (2-8), the characteristic velocity is constrained to always obey  $\vartheta = -(u_t/u_x)$ . With the expression for *u* from (2-10), an expression for characteristic velocity can be found using basic rules of differentiation.

$$\vartheta = x_b'(t) + \frac{x_b(t) - x}{t}.$$

(2-12)

From (2-12) it is clear that when the reference point  $x = x_b(t)$  then the characteristic velocity is  $\vartheta = x'_b(t)$  as expected. Therefore, the proposed approximate PDE in (2-9) can represent ion-migration accurately for an observer located at the accumulation boundary  $x_b(t)$ .

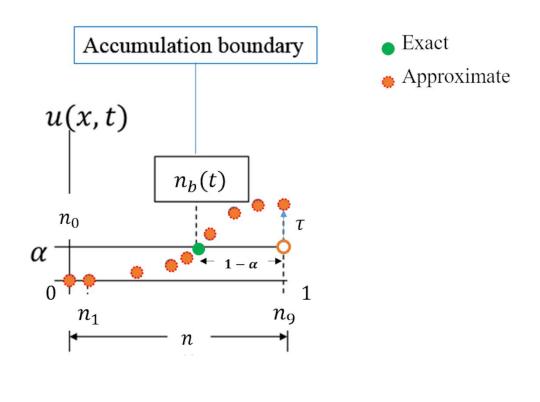

The third term in (2-8) that has been ignored in the simplification is the single, quantifiable source of error. Fig. 2.3 visualizes the exact and approximate model regions for the PDE in (2-9). The governing equation (2-9) models the ion-boundary exactly. The evolution of ions around the ion-boundary will be approximate.

Fig. 2.3 Exact and approximate regions of vacancy evolution.

With the expression for  $\vartheta$  from (2-12), the error (third) term can be deduced as,

$$u \,\vartheta_x = -\frac{u}{t}.\tag{2-13}$$

The error term becomes small for any reason that causes simulation time to be large such as,

- large device length,

- low ion mobility or

- low programming voltage.

The first two conditions can be enforced through manufacturing restrictions and the third can be achieved by limiting test voltage.

#### 2.3.4 Solution verification

This sub section verifies the proposed solution (2-10) in the context of the PDE (2-9). Constants are also evaluated by using known initial and boundary conditions.

## 2.3.4.1 Determining a

It is known that  $u(x, 0) = \alpha$ ; which is a fundamental assumption in the derivation. The flux or integral of programming voltage is zero. Substituting this information into (2-10) produces  $u = (1 + a e^{-f_0 0 (n - n_b(t))})^{-1}$  which can be equated to  $\alpha$ .

$$\alpha = \frac{1}{1+a}.$$

(2-14)

$$a = \frac{1 - \alpha}{\alpha} \tag{2-15}$$

#### 2.3.4.2 Boundary conditions

The boundary condition requires that at  $t \to \infty$ , the ions should accumulate toward an end plate, yielding zero at the evacuating side and the maximum normalized concentration of unity at the accumulating side. Equation (2-16) checks the ion concentration at infinite time at the evacuating (left) side of the device and (2-17) evaluates ion concentration at the accumulating (right) side of the device.

$$u(0,\infty) = \frac{1}{1+a e^{-f_0 \infty \left(0 - n_b(t)\right)}} = \frac{1}{1+a e^{\infty}} = 0$$

(2-16)

$$u(1,\infty) = \frac{1}{1+a \ e^{-f_0 \infty (1-n_b(t))}} = \frac{1}{1+a \ e^{-\infty}} = 1$$

(2-17)

The boundary conditions stand validated.

#### 2.3.4.3 Dimensionality

The dimensions check ensures that the expression for the solution is balanced and unitless in this case. Assigning dimensions within square brackets as is convention and with reference to (2-11),

$$u(n,t) = \frac{1}{1+a e^{-f_0 \phi \left(n-n_b(t)\right)}} = \frac{[]}{[]+[]e^{-[v^{-1}s^{-1}][vs][]}} = [].$$

(2-18)

The solution is dimensionless as expected.

#### 2.3.4.4 Back substitution

Back substitution is guaranteed to pass because of the modeling approach that the characteristic velocity  $\vartheta$  is always computed from  $-\frac{u_t}{u_x}$ . For the model to be reasonable, the only requirement is that the function that represents u must be chosen such that it satisfies empirical observation.

## 2.4 Expressions for Memristor Characteristics

This subsection derives expressions for memristor characteristics, from the computational model.

### 2.4.1 Computational framework

In order to plot the derived expressions, variable values are needed. To ensure consistency, the following values are always used. Only values that differ from these nominal assignments are called out where necessary.

| # | Parameter                    | Symbol | Units            | Nominal value            |

|---|------------------------------|--------|------------------|--------------------------|

| 1 | Ion concentration            | α      | $m^{-3}$         | 0.2                      |

| 2 | Ion mobility                 | μ      | $\frac{m^2}{Vs}$ | 10 <sup>-15</sup>        |

| 3 | Device length                | d      | $\frac{VS}{nm}$  | 32                       |

| 4 | Fresh device resistance      | γ      | Ω                | 100                      |

| 5 | Computational aid            | η      | -                | 0                        |

| 6 | Computational aid            | р      | -                | 0.99                     |

| 7 | Computed flux                | φ      | V s              | $\int_{t=0}^{T} v(t) dt$ |

| 8 | Calculated natural frequency | $f_0$  | Hz               | 0.977                    |

Table 2.1 Table of default parameter values.

In Table 2.1, the natural frequency of the default memristor is calculated using  $f_0 = \frac{\mu}{d^2} = 0.977 \sim 1$  Hz. The dimensions of  $\frac{\mu}{d^2} \left[ \frac{L^2}{V s} \frac{1}{L^2} \right]$  is Hz/V. However, it is possible to cancel the  $V^{-1}$  dimension with the voltage dimension of flux  $\emptyset$  [V s]; thereby enabling  $f_0$  to be written as a pure frequency.

#### 2.4.2 Accumulation boundary

In order to use (2-11) as a solution for ion evolution,  $n_b(t)$  must be known. Integrating (2-11) over the length of the device at any time will yield the total vacancy count within the device; which must equal the original  $\alpha$ . Equating the integral to  $\alpha$  and solving for the only unknown results in an expression for  $n_b(t)$ . In (2-19), all quantities are known except  $n_b(t)$ .

$$\int_{n=0}^{1} \frac{1}{1+a \ e^{-f_0 \phi(n-n_b(t))}} dt = \alpha$$

(2-19)

The computer algebra system (CAS) Mathematica is used to find the solution.

$$n_b(\phi) = \frac{1}{f_0 \phi} \ln\left(\frac{\alpha}{\alpha - 1} \frac{e^{f_0 \phi \alpha} - e^{f_0 \phi}}{e^{f_0 \phi \alpha} - 1}\right)$$

(2-20)

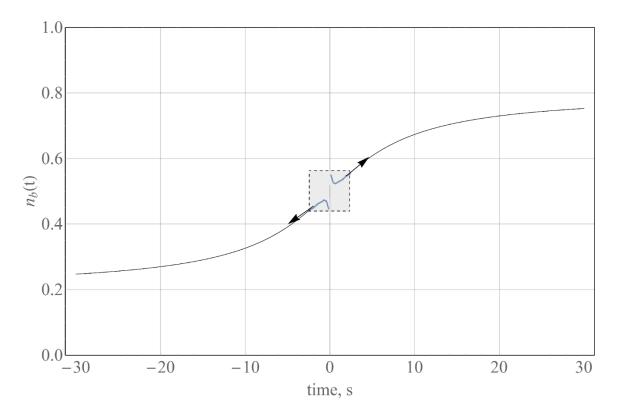

In (2-20),  $\phi = v t$  with v representing a DC voltage and t is time. Fig. 2.4 plots the evolution of (2-20). Variable values used for the plot are the normalized  $\alpha = 0.2$ ,  $f_0 = 1$  and v = 1. Around the origin, each half of the plot shows the ion boundary evolving asymptotically toward either end. This is equivalent to transiting from ST0 to ST1' or ST1 in Fig. 2.1. The initial entry of the ion-boundary into device is shown within the grey bounding box and the direction of travel is shown with the arrow. The significance of the direction reversal of  $n_b(t)$  after initial entry into the device is that it contributes to the transient active nature of this seemingly passive device; as will be explained in later in 5.7 Negative resistance explained.

Fig. 2.4 Ion boundary evolution

#### 2.4.3 Vacancy concentration

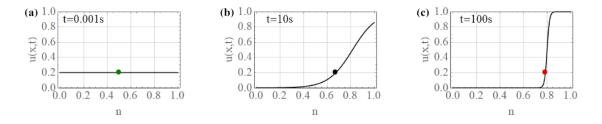

Solution (2-11) works with (2-20) to generate the ion evolution profile. Fig. 2.5 plots ion evolution in a device with 1 V applied across the terminals. The y-axis is normalized concentration  $0 \le u \le 1$ , while the x-axis is the normalized length along the device  $0 \le n \le 1$  where n = x/d. Each plot marks the location of the accumulation boundary with a dot. The device progressively enters high resistance in the sequence Fig. 2.5 (a) – (c).

Fig. 2.5 Ion evolution along the normalized length of the memristor device.

#### 2.4.4 Resistance

This subsection derives the device resistance from ion migration. Low resistance is associated with ions distributed evenly throughout the device. The resistance at any location within the device is defined as,

$$r(x,t) = \frac{\gamma}{1+\eta - p \, u(x,t)}.$$

(2-21)

In (2-21),  $\gamma$  is the resistance of a fresh device with no vacancies or ions,  $\eta$  is a computational knob to prevent the expression from evaluating to infinity in case p u(x, t) evaluates to unity, and p is a computational knob to guarantee that u(x, t) is constrained to less than unity. The resistance across the device terminals can be determined by integrating (2-21) over  $0 \le x \le d$  or its normalized form  $0 \le n \le 1$ .

$$R(t) = \int_{n=0}^{1} r(n,t) \, dn \tag{2-22}$$

The computation was done with Mathematica. The result can be expressed as the sum of two resistors  $R_1(t)$  and  $R_2(t)$  quite simply by partial fraction decomposition.

$$R_{1}(t) = \frac{p^{2} \ln(p^{2} \left(-e^{\frac{\alpha f_{0} \phi}{p}}\right) + e^{f_{0} \phi} + p^{2} - 1)}{f_{0} (p^{2} - 1)\phi} - \frac{1}{p^{2} - 1}$$

(2-23)

$$R_{2}(t) = -\frac{p^{2}\log(\left((1-p^{2})e^{f_{0}\phi}-1\right)e^{\frac{f_{0}\phi(\alpha-p)}{p}}+p^{2})}{f_{0}(p^{2}-1)\phi}$$

$$R(t) = R_{1}(t) + R_{2}(t)$$

(2-25)

(2-25)

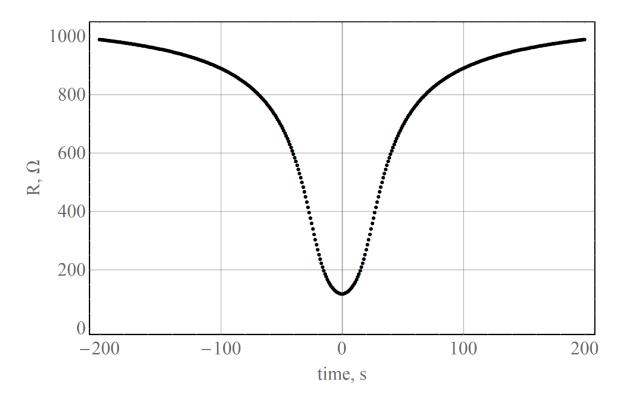

Equations (2-23) and (2-24) use  $\gamma = 1$ ,  $\eta = 0$ ,  $\phi = (v t)$  and  $\frac{\mu}{d^2} = f_0$ . Although in this case  $\phi = (v t)$ , the general representation must be  $\phi = \int_{t=0}^{T} v(t) dt$ . Equation (2-25) represents the composite device resistance and is the sum of the individual components. Fig. 2.6 plots (2-25) with p = 0.99.

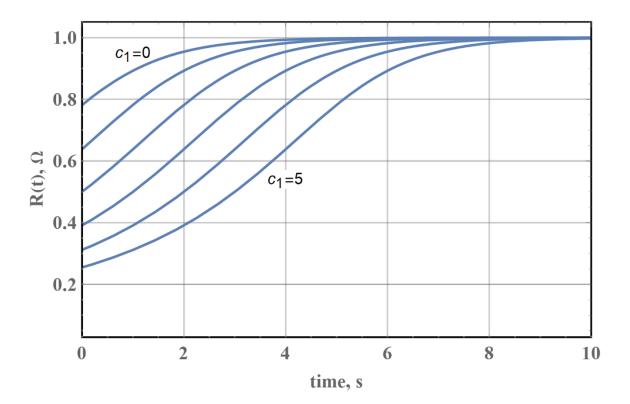

Fig. 2.6 Device resistance as a function of time.

Fig. 2.6 shows resistance evolving from a high value to low and back to high resistance as proposed in Fig. 2.1. The notable result is that the expression for resistance derived from (2-9) has two computable parts (2-25), like the DVR based rheostat from HP.

## 2.4.5 I-V curves

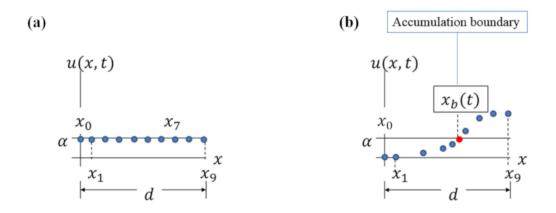

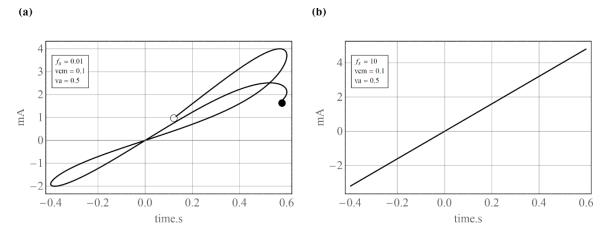

Current-voltage curves are almost always presented as a signature of memristance. Memristance manifests as lobes in the I-V curve where a specific stimulus results in two responses depending on the direction in which the voltage sweep occurs. Fig. 2.7 plots the simulated current through the device, for a sinusoidal forcing function of v(t) = 0.1 +0.5 sin ( $\omega t$ ) and all nominal values from Table 2.1. The unfilled dot indicates the start of while the black filled dot indicates the end of the trace.

Fig. 2.7 Simulated memristor I-V curves demonstrating the three fingerprints.

Fig. 2.7 (a) shows the I-V plot for 1.3 cycles of the input stimulus which has a dc offset  $v_{cm}$  of 100mV. The device natural frequency is about 1 Hz and the forcing frequency is indicated by the variable  $f_s$  in the figures. The dc offset is obvious from the asymmetry of the trace along the x and y axis. The first lobe in quadrant 1 is large and shows the device starting in the low-resistance state and entering high resistance. The second lobe in quadrant 3 is much smaller because the dc offset causes the device resistance to increase even when the stimulus is negative. The third lobe in quadrant 1 has a low resistance that is higher than the low resistance associated with the first lobe. The simulation is terminated just prior to reaching the origin. Fig. 2.7 (a) exhibits fingerprint 1 which expects a pinched hysteresis loop as detailed in sub section 1.3.3.1.

Fig. 2.7 (b) uses a stimulus at 10 times the natural frequency of the device; common-mode and amplitude unchanged from Fig. 2.7 (a). The pinched loop has decreased in area compared to panel (a) satisfying fingerprint 2 from sub section 1.3.3.2. In this case the I-V curve has completely collapsed to a straight line, also satisfying fingerprint 3 from sub section 1.3.3.3.

Given that the resistance of a fresh device is about 100  $\Omega$ ; the plots correctly demonstrate a maximum current of 4 mA in agreement with the calculation  $i = 0.5 \frac{V}{100} \Omega$ . The simulated maximum current is lower because the device is always responding to the 100 mV common mode that constantly pushes it into the high resistance state.

In summary, the computational model can demonstrate the three fingerprints of memristors.

#### 2.4.6 Switching time

Switching or transition time is the time it takes for a memristive device to transition from low resistance to high resistance or vice versa. Symbolic evaluation of transition time from (2-22) is impossible. Therefore, an approximate but novel approach is adopted to estimate the transition time. Assume that Fig. 2.8 shows the evolved state of vacancies in a device.

Fig. 2.8 Model for estimating transition time. 33

It is proposed that the time it takes for the ion concentration at the position n = 1 to evolve from its original value of  $u(1,0) = \alpha$  to  $u(1,\tau) = 1$  is the transition time  $\tau$ . Constraining the model to work with the resistance at a single position enables the calculations to use (2-21). Low resistance is estimated by setting  $u = \alpha$ . For convenience assume that the computational aids are assigned  $\eta = 0$  and p = 1.

$$r_{LO} = \frac{\gamma}{1 - \alpha} \tag{2-26}$$

Similarly, the high resistance is estimated by,

$$r_{HI} = \frac{\gamma}{1 - u(1,\tau)}.$$

(2-27)

Defining resistance ratio as rr,

$$rr = \frac{r_{HI}}{r_{L0}} = \frac{(1-\alpha)}{1-u(1,\tau)}.$$

(2-28)

From (2-11),  $u(n,t) = \frac{1}{1+a e^{-f_0 \phi \left(n-n_b(t)\right)}}$ . It follows that,  $u(1,\tau) = \frac{1}{1+a e^{-f_0 \phi \left(1-n_b(\tau)\right)}}$ ;

where  $n_b(\tau) \sim (1 - \alpha)$ . Because the concept of transition time applies only with DC excitation,  $\phi = V \tau$ . Substitute for  $u(1, \tau)$  in (2-28) and simplify.

$$rr = (1 - \alpha) + \alpha e^{\alpha f_0 V \tau}$$

(2-29)

Transition time is obtained after simple algebraic manipulation.

$$\tau = \frac{1}{f_0 V} \left( \frac{1}{\alpha} \ln \left( \frac{rr}{\alpha} - \frac{1 - \alpha}{\alpha} \right) \right)$$

(2-30)

Expression (2-30) is the first time in literature that a relationship between transition time vacancy concentration has been quantified [33] and discussed in additional detail in [34]. The salient observations from (2-30) follow.

- Switching time is inversely proportional to the programming voltage. A device can benefit from being operated at a higher voltage to increase its operating speed; limited by the breakdown voltage across the MIM sandwich.

- Switching time is inversely proportional to the device natural frequency f<sub>0</sub>.

Recalling that natural frequency itself is f<sub>0</sub> = μ/d<sup>2</sup>, the inference is that switching is inversely proportional to ion mobility and directly proportional to the square of device length. These findings agree with the linear estimation by Strukov et al. [38], Biolek et al. [27] and Batas et al. [16].

The additional term in (2-30) reveals the influence of ion concentration on transition.

- The nonlinear dependence of switching time is dominated by ion concentration  $\alpha$ .

- Switching time is inversely proportional to  $\alpha$  [34], except at bounding values of  $\alpha$ .

Consider (2-30) with the substitution  $rr = \frac{r_{HI}}{r_{LO}}$ ; where  $r_{HI} = \frac{\gamma}{1-p u(n,\tau)}$  and  $r_{LO} = \frac{\gamma}{1-\alpha}$ . This leads to an expression entirely in p and  $\alpha$ .

$$\tau = \frac{1}{f_0 V} \left( \frac{1}{\alpha} \ln \left( \frac{p}{1-p} \frac{1-\alpha}{\alpha} \right) \right)$$

(2-31)

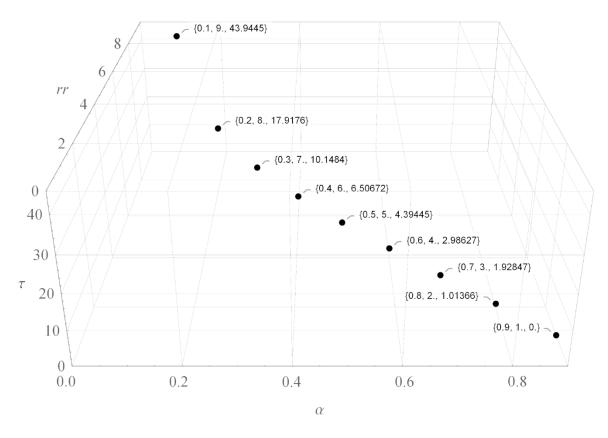

Although *p* is usually assumed to be 1 for convenience, it is a computational assist that tunes the model for Coulomb repulsion or van der Waals forces that *disallow*  $u(1, \infty) = 1$  [38]. A practical setting for *p* may be  $0.8 \le p \le 1$ . Similarly, (2-29) can be expressed in only *p* and  $\alpha$ . Fig. 2.9 plots (2-31) and (2-32).

$$rr = \frac{1-\alpha}{1-p} \tag{2-32}$$

Fig. 2.9 Relationships between ion concentration, switching time and resistance ratio.

The data points in Fig. 2.9 are annotated with  $(\alpha, rr, \tau)$  in that order. When ion concentration  $\alpha$  increases, the resistance ratio and transition time decrease. Therefore, it is not possible to decrease transition time without impacting the resistance switching range for a given chemical species unless ion-mobility, device length or programming voltage are manipulated [33].

## 2.4.7 Switching energy

Energy awareness is paramount in any modern analog or digital application. From (2-25),

$$E = \int_{t_0}^{t_1} \frac{V^2}{R(t)} dt = \int_{t=0}^{\tau} \frac{V^2}{R(t)} dt.$$

(2-33)

A memristor is referred to as being on the shelf or unused whenever it has zero volts across the device terminals. The computational model in this dissertation assumes that vacancies accumulate and dissipate in time, with some spatial distribution profile along the device length. This is similar to the heat redistribution in a thermally insulated rod. The insulation is analogous to enforcing vacancy conservation which guarantees that vacancies cannot exit the memristor.

Shelf life is modeled with the following "heat" equation.

$$u_t + \mathcal{D} \, u_{xx} = 0 \tag{2-34}$$

The second term in (2-34) models ion dispersal due to concentration gradients. Coefficient  $\mathcal{D}$  is the diffusion constant. This PDE can be solved symbolically using Fourier analysis [33].

$$u(x,t) = A_0 + \sum_{i=1}^{\infty} A_n \cos\left(\frac{i\pi x}{d}\right) e^{-\left(\frac{i\pi}{d}\right)^2 \mathcal{D} t}$$

(2-35)

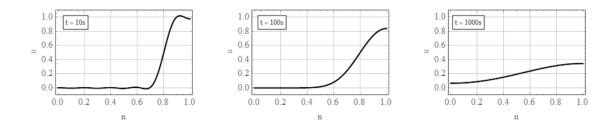

In (2-35)  $A_0$  and  $A_1$  are coefficients that can be determined using a knowledge of the initial conditions. Variable *i* is the iterator,  $\mathcal{D}$  is diffusion coefficient, *d* is device length. Literature suggests that memory resistance retention can stretch from 5 to 11 years [39], [40], [41]. Consider Fig. 2.10 which demonstrates the dissipation of ions during shelf time. The initial distribution of vacancies was described by  $f(n) = \frac{1}{1+e^{s(n-n_b(t))}}$ . Given that the device must be in its high resistance state at the start of the simulation,  $n_b(t) = 1 - \alpha$ . The variable *s* represents slope of the vacancy profile. This slope is a function of the accumulated flux from prior programming, namely  $s = f_0 \phi$ .

Fig. 2.10 Ions dissipating during shelf time.

The three panels of Fig. 2.10 demonstrate that vacancies dissipate over time solely due to the concentration gradient. Normalized simulation parameters were  $D/d^2 = 100\mu$ ,  $\alpha = 0.2$  and  $s = 100 V \cdot s$ .

While an ideal device modeled by (2-9) is non-volatile, a more practical volatile device can be modeled by combining terms of (2-9) and (2-34).

$$u_t + \vartheta \, u_x + \mathcal{D} \, u_{xx} = 0 \tag{2-36}$$

From the discussions up to this point, it should be clear that during programming of a memristor, the active transport of ions can be modeled by the first two terms of (2-36). Memristive un-programming due to disuse can be modeled by equating the sum of the first and third terms to zero.

## 2.5 Model Validation

Switching time is a convenient and often reported parameter against which the model in this dissertation can be benchmarked. Switching speed is a function of ion mobility, temperature, voltage and device length. Second order effects like surface roughness at the interfaces, nonuniformity of the electric field between the plates, local heating effects that affect mobility etc. are expected to play a significant role in determining device switching time. Only a numerical approach can tackle the problem when second order effects are considered. Such methods are outside the scope of this dissertation. The following calculations assume room temperature, since it is not usually reported. The following results based on (2-30) are published [33].

|    |             |                  |          |                       |          | <b>Transition time</b> $\tau(s)$ |         |

|----|-------------|------------------|----------|-----------------------|----------|----------------------------------|---------|

| #  | Reference   | Oxide            | Volts(V) | <sup>1</sup> Mobility | Reported | This dissertation                | % Error |

| 1a | [23] Nardi  | $HfO_x$          | 1.2      | 10-08                 | 04 μ     | 03.20 μ                          | -20     |

| 1b | "           | "                | 1.0      | 0.22x10 <sup>-8</sup> | 15 μ     | 20.00 µ                          | 33      |

| 1c | "           | "                | 0.8      | 0.19x10 <sup>-8</sup> | 20 µ     | 21.70 µ                          | 8.5     |

| 2  | [5] Strukov | TiO <sub>2</sub> | 1.0      | 10-14                 | 10 m     | 10.00 m                          | 0.0     |

| 3  | [42] Lu     | Ag/a             | 3.2      | 10 <sup>-08</sup>     | 1.2 m    | 1.180 m                          | 1.6     |

|    |             | -Si              |          |                       |          |                                  |         |

| 4  | [29] Biolek | TiO <sub>2</sub> | 1.0      | 10-14                 | 500 m    | 448.0 m                          | 10.4    |

Table 2.2 Validation of transition time against independent empirical data.

<sup>1</sup> Mobility was estimated from among various sources. Rows 1b and 1c used arbitrarily scaled mobility to accommodate the dependence on electric field.

## 2.6 Chapter Summary

The computational ion transport model presented in this chapter is derived from the traditional transport equation. Long channel length, low mobility or programming voltage are the justifications for ignoring a term in the PDE that computes the gradient of the characteristic wave velocity. This simplification permits a Heaviside step or logistic function like symbolic solution. This solution to the governing equation is validated against the PDE. The solution is then used to demonstrate and derive expressions for a variety of memristor characteristics; each showing good correlation to the works of independent researchers. The problem of memory volatility is addressed by observing a correspondence between the popular heat dissipation problem in physics and ion dissipation in a concentration gradient. The heat equation is reformulated with variables appropriate to vacancy migration and solved symbolically. The resulting solution is shown to exhibit ion dissipation as expected. Largely, this chapter quantified the memristor life cycle with governing equations and solutions.

# **3** Computational Logistic Model

This chapter presents the transition from ion transport to abstract logistic modeling. The discussion is substantially drawn from [43] where we first reported the development and evaluation of this technique.

## 3.1 Background

Expressions such as (2-10) in the computational ion transport model are very similar to a smooth Heaviside step function [36] or the logistic/sigmoid function [37]. These functions take on the same shape as the ion evolution profile. Abstract functions have the advantage that they decouple a model from the underlying operating mechanism. The focus is on generating life-like responses with none of the physics. Abstract models can be computationally simpler than physical models, provide a level of generality and sometimes clarity.

Model abstraction is not new. In their work associating memristive response to Abel, Riccati and Bernoulli dynamics, Biolek et al. propose that sigmoidal functions may be useful in representing memristor behavior [30]. A sigmoidal model from Saminathan et al. is also known [44]. Saminathan uses the sigmoid like a window function f(w(t)) to modulate the HP equations as shown in (1-8). Ascoli et al. study local-activity in memristors as observed by HP, using polynomial functions [45]. Corinto et al. have presented hypergeometric and gamma function solutions to the HP equations [28]. These researchers have laid the foundations for studying memristors from a non-linear dynamics perspective using abstract modeling.

### 3.2 Motivation

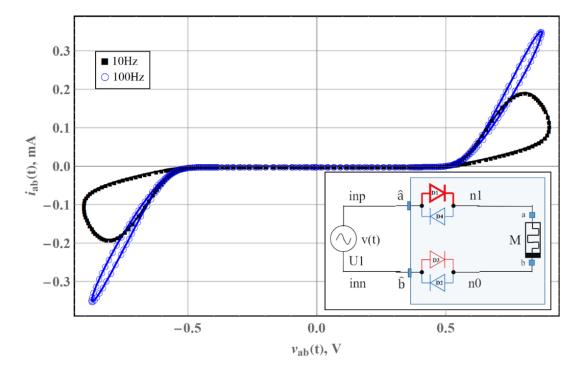

Memristors have been reported to exhibit chaotic response even in contemporary literature [46], [47], [48]. This property has purportedly been used in secure communications [48]. Although the computational ion transport model *does* exhibit the presence of an active phenomenon within the device the solution is well behaved and being first order, does not exhibit any chaotic response. While fractional calculus has been used to demonstrate memristive chaos [49], [50], these techniques tend to be deeply mathematical and are inaccessible to the general circuit design community. Miranda et al. have demonstrated memristive hysteresis using a double diode based logistic model [51], [52]. Corinto et al. have presented some research based on traditional nonlinear dynamics [53], [54]. With these efforts as backdrop, this dissertation explores the ability of the standalone logistic equation to exhibit memristive qualities including chaotic response.

#### 3.3 The Logistic Function

The ion evolution profile along the device resembles a traveling logistic function as seen in Fig. 2.5, where a shallower distribution is associated with low resistance and a steeper distribution maps to high resistance. Consider the following textbook logistic function which has been slightly modified to include memristor parameters.

$$R(t, n_b(t)) = s \frac{R_{max}}{1 + c \, e^{-m \, f_0 \, n_b(t) \int_{t=0}^T v(t) \, dt}}$$

(3-1)

In (3-1),  $R(t, n_b(t))$  is the memory resistance as a function of time and the location of the accumulation boundary,  $R_{max}$  is the maximum possible resistance of the device from empirical observations, c is an arbitrary constant is determined by the minimum resistance, m and s are free variables that can tune the device response,  $f_0$  is the natural frequency of the device and  $\int_{t=0}^{T} v(t) dt$  calculates electric flux. Variable c can be determined by equating  $R(t, n_b(t))|_{t=0}$  to a numerical value for  $R_{min}$  and solving. Variable m can be arbitrarily chosen to match the device's temporal response from empirical data. Variable s is useful for arbitrary scaling of the amplitude of the function.

It was determined through simulations that computations can be simplified by disregarding  $n_b(t)$  and relying on *m* to tune the model.

$$R(t) = s \frac{R_{max}}{1 + c \, e^{-m f_0} \int_{t=0}^{T} v(t) \, dt}$$

(3-2)

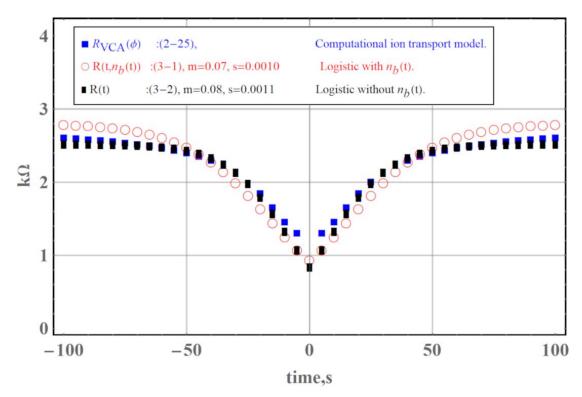

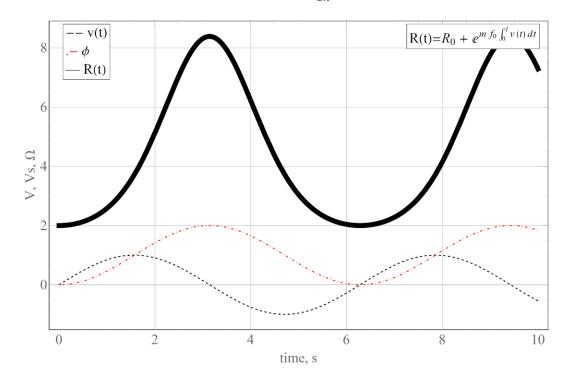

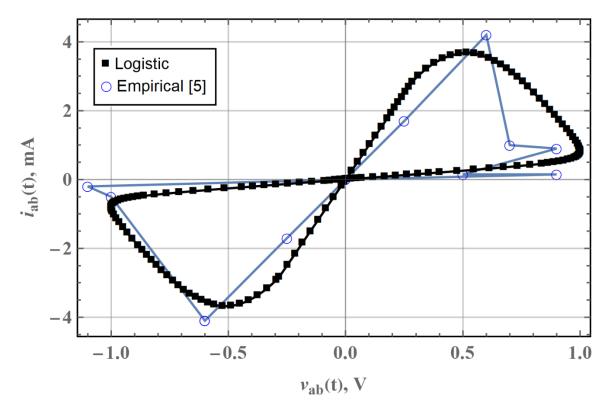

Equation (3-2) is identical to (3-1) except for the discarded  $n_b(t)$  term in the exponent of e in the denominator. Consider Fig. 3.1 wherein the temporal response of (2-25), (3-1) and (3-2) are compared. Fig. 3.1 used  $R_{max} = 2.5k \Omega$ ,  $f_0 = 1 Hz$ , c = 2,  $\alpha = 0.2$ , p = 0.9 and a programming voltage of 1 V DC. A careful choice of tuning parameters m and s produced an acceptable match between the computational ion transport and the two variations on the computational logistic model. The conclusion is that the logistic form in (3-2) without any reference to the ion boundary is sufficient to demonstrate memristive characteristics. It is also possible to relate some of the free variables to the computational ion transport model. For example c can be found by equating  $R(0)_{(3-2)}$  to  $R(0)_{(2-21)}$ ; where

the subscript are equation numbers. Solving  $s \frac{R_{max}}{1+c} = \frac{\gamma}{1-\alpha}$ , for *c* produces  $c = \frac{s R_{max}(1-\alpha)-\gamma}{\gamma}$ . Additionally, if  $R_{max} = \frac{\gamma}{1-p}$ , then it is possible to reduce further as  $c = s \frac{(1-\alpha)}{(1-p)} - 1$ . Validation with an I-V curve is reserved for the SPICE modeling section.

Fig. 3.1: Transient resistance-time curves comparing computational ion transport, logistic and simplified logistic models.

## 3.4 The Logistic Equation

The sigmoid function is a solution to the ODE  $y' = \mu y(1 - y)$  [37] where y is a function of time and  $\mu$  is an arbitrary constant. Associate y with R and evaluate the left-hand side (LHS) of the said ODE for R from (3-2).

$$R' = \frac{c \, m \, s \, f_0 \, R_{max} \, v(t) \, e^{m \, f_0 \, \int v(t) \, dt}}{\left(c + e^{m \, f_0 \, \int v(t) \, dt}\right)^2}.$$

(3-3)

The RHS can be evaluated similarly.

$$\mu R(1-R) = \frac{\mu s R_{max} \left(1 - \frac{s R_{max}}{1 + c e^{-m f_0 \int v(t) dt}}\right)}{1 + c e^{-m f_0 \int v(t) dt}}$$

(3-4)

To be valid, equations (3-3) and (3-4) must be identical for some value of  $\mu$  that can be solved for. The governing logistic equation can be written as follows.

$$R' = \mu R(1-R): \mu = \frac{c m f_0 v(t)}{c + (1 - s R_{max}) e^{m f_0 \int v(t) dt}}$$

(3-5)

The leading term  $\mu$  is sometimes called the Malthusian parameter. Equation (3-5) is shown with a general  $\mu(t)$  which simplifies to a constant if the programming voltage is DC. Biolek's research into the Bernoulli Parameter State Map (PSM) resembles (3-5). For v(t) = 1 and  $s = 1/R_{max}$ ,  $\mu$  evaluates to  $\mu = m f_0$ , a constant.

## 3.5 The Logistic Map

Memristor models to date such as the HP [5], VCA [33], [34], VTEAM [55] etc. are differential equations of the first order. First order models do not readily exhibit sensitive dependence on initial conditions. Memristive circuits on the other hand have been reported to exhibit a rich variety of dynamics by Strukov [5], Petras [49] and Corinto et al. [53], [54]. The logistic map makes it feasible to model the memristor's purported sensitivity to initial conditions. A map is a discretized version of a continuous function. Consider the following first step where the function is replaced by the  $n^{th}$  iterate.

$$\frac{R_{n+1}-R_n}{\Delta t} = \mu R_n (1-R_n) \tag{3-6}$$

Simple algebraic manipulation produces an expression for  $R_{n+1}$ .

$$R_{n+1} = R_n (1 + \mu \Delta t) - \mu R_n^2 \Delta t \tag{3-7}$$

Let  $\hat{\mu} = (1 + \mu \Delta t)$  from which it follows that  $\Delta t = \frac{\hat{\mu} - 1}{\mu}$ . Substituting these into (3-7),

$$R_{n+1} = \hat{\mu} R_n \left( 1 - \left( 1 - \frac{1}{\hat{\mu}} \right) R_n \right)$$

(3-8)

Let  $\hat{R}_n = \left(1 - \frac{1}{\hat{\mu}}\right) R_n$ . Then it also follows that  $R_n = \frac{\hat{\mu}}{(\hat{\mu} - 1)} \hat{R}_n$ ; implying that  $R_{n+1} = \frac{\hat{\mu}}{(\hat{\mu} - 1)} \hat{R}_{n+1}$ . Make these substitutions into (3-9).

$$\hat{R}_{n+1} = \hat{\mu} \, \hat{R}_n \big( 1 - \hat{R}_n \big) \tag{3-9}$$

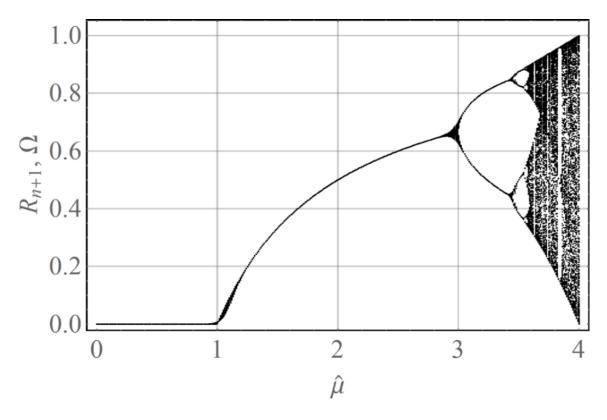

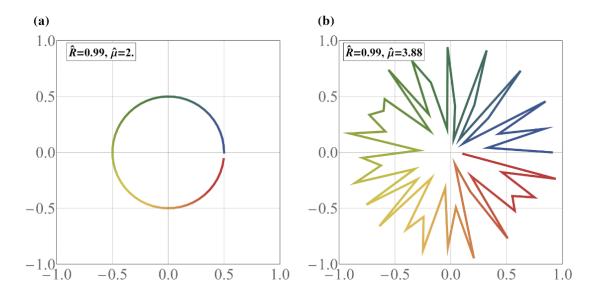

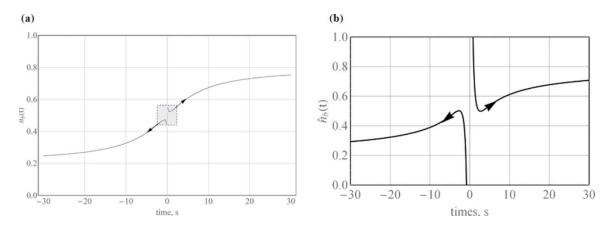

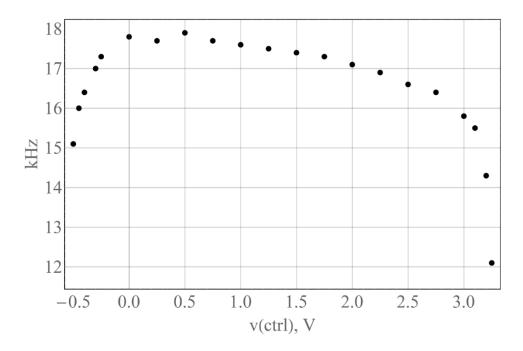

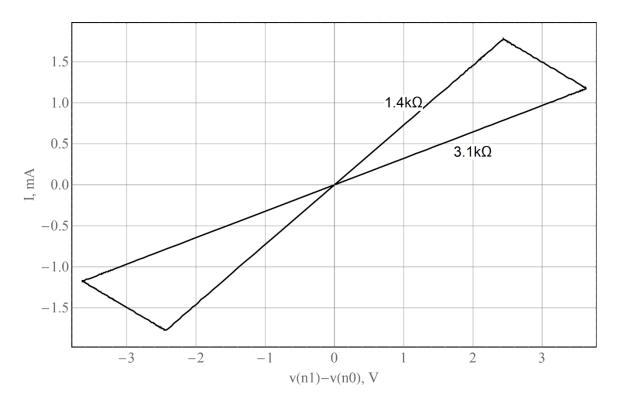

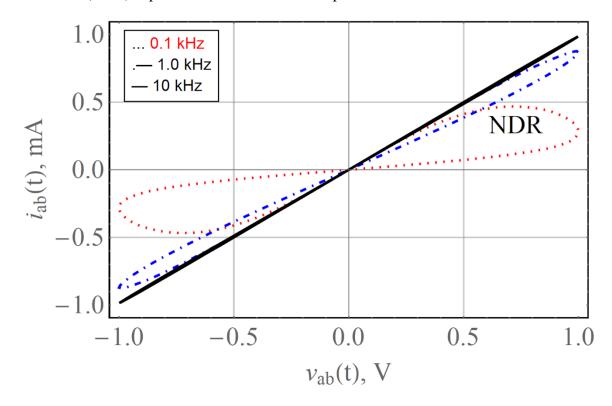

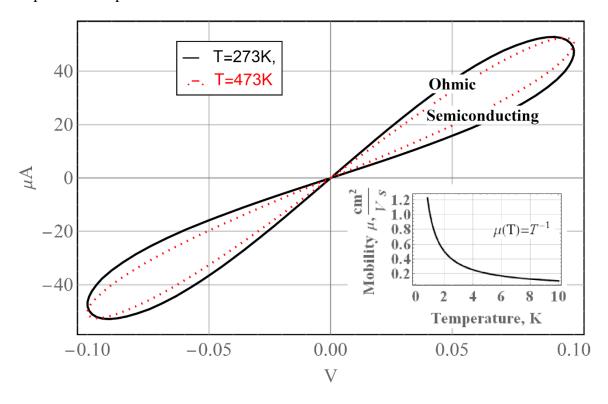

Equation (3-9) is the discrete analogue of (3-5) and is a textbook study for chaotic responses [56]. Parameter  $\hat{\mu}$  elicits oscillations for different values. Traditionally an orbit diagram accompanies (3-9). The orbit diagram plots  $\hat{R}_{n+1}$  against the independent variable  $\hat{\mu}$ . Due to sensitivity to initial conditions, any given  $\hat{\mu}$  will display many  $\hat{R}_{n+1}$  for the first few iterations, subsequently settling down to a more finite set as the number of iterations increase. Consider the orbit plot in Fig. 3.2 generated with a normalized seed of  $R_n = 0.99$ , where the first 30 of 300 iterations were discarded. With  $s = 1/R_{max}$ ,  $\hat{\mu} = m f_0$ , where  $\hat{\mu}$  will be influenced by the physical parameters that determine the device natural frequency; namely device length, localized and variable ion mobility and potential gradients. Therefore, the variability in  $\hat{\mu}$  is a source of the chaotic response.