#### Wright State University

#### **CORE Scholar**

Browse all Theses and Dissertations

Theses and Dissertations

2022

### Low-Power, Low-Cost, & High-Performance Digital Designs: Multibit Signed Multiplier design using 32nm CMOS Technology

N V Vijaya Krishna Boppana Wright State University

Follow this and additional works at: https://corescholar.libraries.wright.edu/etd\_all

Part of the Engineering Commons

#### **Repository Citation**

Boppana, N V Vijaya Krishna, "Low-Power, Low-Cost, & High-Performance Digital Designs: Multi-bit Signed Multiplier design using 32nm CMOS Technology" (2022). Browse all Theses and Dissertations. 2643.

https://corescholar.libraries.wright.edu/etd\_all/2643

This Dissertation is brought to you for free and open access by the Theses and Dissertations at CORE Scholar. It has been accepted for inclusion in Browse all Theses and Dissertations by an authorized administrator of CORE Scholar. For more information, please contact library-corescholar@wright.edu.

# LOW-POWER, LOW-COST, & HIGH-PERFORMANCE DIGITAL DESIGNS: MULTI-BIT SIGNED MULTIPLIER DESIGNS USING 32NM CMOS TECHNOLOGY

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

By

N V VIJAYA KRISHNA BOPPANA

M.S.Eg., Wright State University, USA, 2014

B.E., Andhra University, India, 2011

2022

Wright State University

Copyright © 2022 All Rights Reserved

N V Vijaya Krishna Boppana @ Wright State University

2022

## WRIGHT STATE UNIVERSITY GRADUATE SCHOOL

July 27, 2022

I HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER MY SUPERVISION BY N V Vijaya Krishna Boppana ENTITLED Low-Power, Low-Cost, & High-Performance Digital Designs: Multi-bit Signed Multiplier Designs using 32nm CMOS Technology BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy.

|                                 | Saiyu Ren, Ph.D.              |

|---------------------------------|-------------------------------|

|                                 | Dissertation Director         |

|                                 | W. 1 . 1.0 . 11 . D. D. F.    |

|                                 | Michael Saville, Ph.D., P.E.  |

|                                 | Chair, Electrical Engineering |

|                                 | Barry Milligan, Ph.D.         |

|                                 | Dean of the Graduate School   |

| Committee on Final Examination: |                               |

| Daymand E Siford Dh D           |                               |

| Raymond E. Siferd, Ph.D.        |                               |

| Henry Chen, Ph.D.               |                               |

| Marian K. Kazimierczuk, Ph.D.   |                               |

|                                 |                               |

| Yan Zhuang, Ph.D.               |                               |

#### **Abstract**

Boppana, N V Vijaya Krishna. Ph.D., Department of Electrical Engineering, Wright State University, 2022. "Low-Power, Low-Cost, & High-Performance Digital Designs: Multibit Signed Multiplier design using 32nm CMOS Technology"

Binary multipliers are ubiquitous in digital hardware. Digital multipliers along with the adders play a major role in computing, communicating, and controlling devices. Multipliers are used majorly in the areas of digital signal and image processing, central processing unit (CPU) of the computers, high-performance and parallel scientific computing, machine learning, physical layer design of the communication equipment, etc. The predominant presence and increasing demand for low-power, low-cost, and highperformance digital hardware led to this work of developing optimized multiplier designs. Two optimized designs are proposed in this work. One is an optimized 8 x 8 Booth multiplier architecture which is implemented using 32nm CMOS technology. Synthesis (pre-layout) and post-layout results show that the delay is reduced by 24.7% and 25.6% respectively, the area is reduced by 5.5% and 15% respectively, the power consumption is reduced by 21.5% and 26.6% respectively, and the area-delay-product is reduced by 28.8% and 36.8% respectively when compared to the performance results obtained for the state-of-the-art 8 x 8 Booth multiplier designed using 32nm CMOS technology with 1.05 V supply voltage at 500 MHz input frequency. Another is a novel radix-8 structure with 3-bit grouping to reduce the number of partial products along with the effective

partial product reduction schemes for 8 x 8, 16 x 16, 32 x 32, and 64 x 64 signed multipliers. Comparing the performance results of the (synthesized, post-layout) designs of sizes 32 x 32, and 64 x 64 based on the simple novel radix-8 structure with the estimated performance measurements for the optimized Booth multiplier design presented in this work, reduction in delay by (2.64%, 0.47%) and (2.74%, 18.04%) respectively, and reduction in area-delay-product by (12.12%, -5.17%) and (17.82%, 12.91%) respectively can be observed. With the use of the higher radix structure, delay, area, and power consumption can be further reduced. Appropriate adder deployment, further exploring the optimized grouping or compression strategies, and applying more low-power design techniques such as power-gating, multi-Vt MOS transistor utilization, multi-VDD domain creation, etc., help, along with the higher radix structures, realizing the more efficient multiplier designs.

## TABLE OF CONTENTS

| 1 |     | In    | trod  | luction                                                                 | . 1 |

|---|-----|-------|-------|-------------------------------------------------------------------------|-----|

|   | 1.1 |       | Digi  | tal Multiplier                                                          | . 1 |

|   | 1.2 |       | Rese  | earch motivation and objective                                          | . 2 |

| 2 |     | Li    | tera  | ture Review                                                             | 4   |

|   | 2.1 |       | Digi  | tal Multiplier                                                          | . 4 |

|   | 2.2 |       | Mul   | tiplier Architectures                                                   | 5   |

|   | 2   | 2.2.1 |       | Array Multiplier                                                        | 5   |

|   | 2   | 2.2.2 | 2     | Tree Multiplier [6]                                                     | . 7 |

|   |     | 2.2   | 2.2.1 | Wallace Tree Multiplier (WTM) [7]                                       | . 8 |

|   |     | 2.2   | 2.2.2 | Dadda Tree Multiplier [20]                                              | 14  |

|   | 2   | 2.2.3 | 3     | Booth Multiplier                                                        | 20  |

|   | 2   | 2.2.4 | 1     | Baugh-Wooley Two's Complement Signed Multiplier [32]                    | 22  |

|   | 2   | 2.2.5 | 5     | Vedic Multiplier                                                        | 28  |

| 3 |     | O     | ptim  | nization of radix-4 8 x 8 Booth multiplier                              | 30  |

|   | 3.1 |       | Intro | oduction                                                                | 30  |

|   | 3.2 |       | Low   | power-delay-product radix-4 8 x 8 Booth multiplier [42]                 | 31  |

|   | 3.3 |       | Low   | v-cost and high-performance radix-4 8 x 8 Booth multiplier [41]         | 34  |

|   | 3   | 3.3.1 |       | Booth encoder optimization & partial product generation                 | 37  |

|   | 3   | 3.3.2 | 2     | Reduction of Partial Products using Two-Stage Parallel Addition         | 41  |

|   | 3   | 3.3.3 | 3     | B2C optimization                                                        | 45  |

| 4 |     | Pr    | opo   | sed Multiplier Architecture based on radix-8 (3-bit grouping) structure | re  |

| 7 |     | References                                                | 108 |

|---|-----|-----------------------------------------------------------|-----|

| 6 |     | List of Abbreviations                                     | 105 |

|   | 5.4 | Publications                                              | 103 |

|   | 5.3 | Future Work                                               | 102 |

|   | 5.2 | Major Contributions                                       | 101 |

|   | 5.1 | Conclusion                                                | 100 |

| 5 |     | Conclusions and Future Work                               | 100 |

| 4 | 4.5 | Results & Performance Comparison                          | 81  |

| 4 | 4.4 | 64 x 64 signed multiplication using the proposed design : | 75  |

| 4 | 4.3 | 32 x 32 signed multiplication using the proposed design : | 70  |

| 4 | 4.2 | 16 x 16 signed multiplication using the proposed design : | 58  |

| 4 | 4.1 | 8 x 8 signed multiplication using the proposed design:    | 49  |

## LIST OF FIGURES

| FIGURE 1. EXAMPLE OF A BINARY MULTIPLICATION                                  | 5  |

|-------------------------------------------------------------------------------|----|

| Figure 2. 4-bit x 4-bit Array Multiplier                                      | 7  |

| Figure 3. 4-bit x 4-bit Tree Multiplier [6]                                   | 8  |

| FIGURE 4. WALLACE TREE MULTIPLIER USING CARRY SAVE ADDERS [6]                 | 9  |

| FIGURE 5. DOT DIAGRAM FOR AN 8-BIT X 8-BIT WALLACE TREE MULTIPLIER [8]        | 10 |

| FIGURE 6 DELAY DIAGRAM OF AN 8 X 8 WALLACE MULTIPLIER WITH RCA AS A FINAL     |    |

| Adder [8]                                                                     | 12 |

| FIGURE 7. DOT DIAGRAM FOR AN 8-BIT X 8-BIT DADDA TREE MULTIPLIER [8]          | 15 |

| FIGURE 8. DELAY DIAGRAM OF AN 8 X 8 DADDA MULTIPLIER WITH RCA AS FINAL ADDER  |    |

| [8]                                                                           | 18 |

| FIGURE 9 3-BIT GROUPING PERFORMED IN RADIX-4 BOOTH MULTIPLIER                 | 20 |

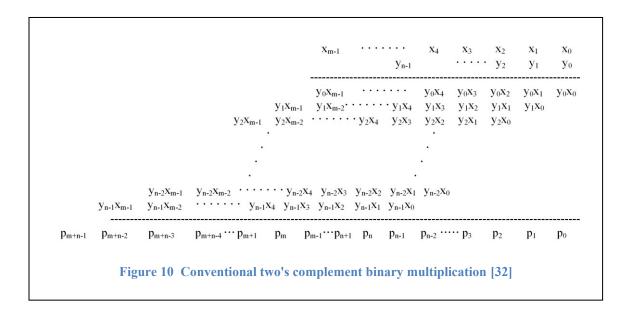

| FIGURE 10 CONVENTIONAL TWO'S COMPLEMENT BINARY MULTIPLICATION [32]            | 23 |

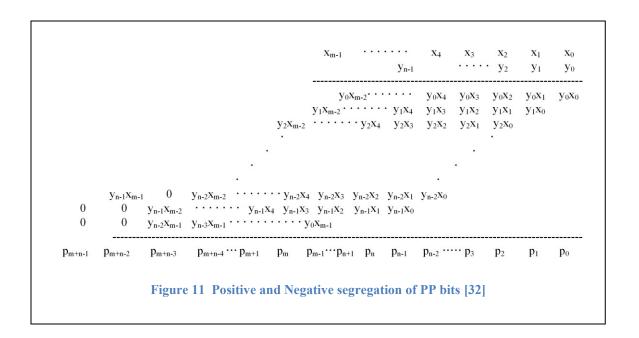

| FIGURE 11 POSITIVE AND NEGATIVE SEGREGATION OF PP BITS [32]                   | 26 |

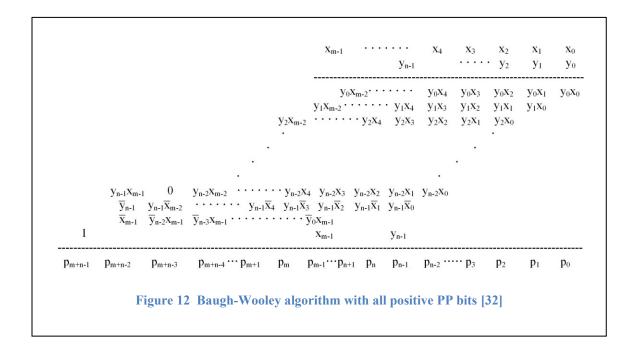

| FIGURE 12 BAUGH-WOOLEY ALGORITHM WITH ALL POSITIVE PP BITS [32]               | 28 |

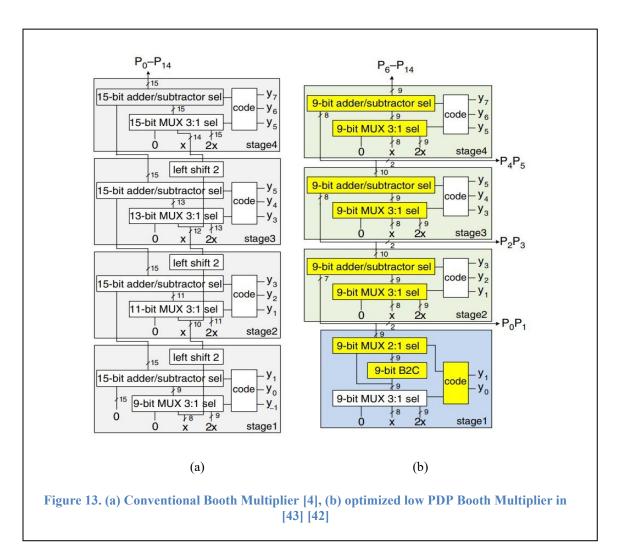

| FIGURE 13. (A) CONVENTIONAL BOOTH MULTIPLIER [4], (B) OPTIMIZED LOW PDP BOOTH |    |

| Multiplier in [43] [42]                                                       | 31 |

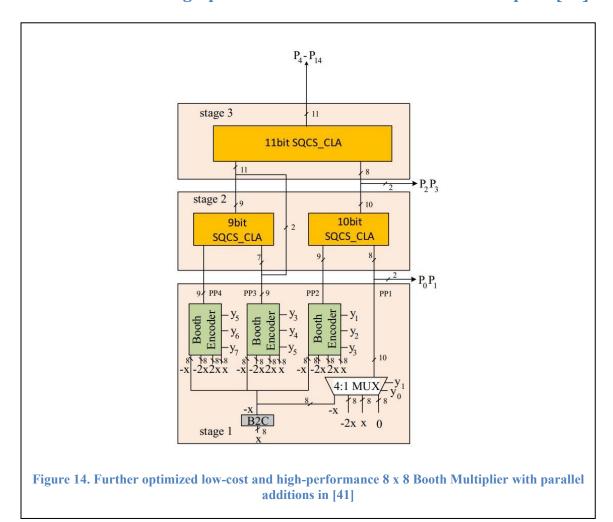

| FIGURE 14. FURTHER OPTIMIZED LOW-COST AND HIGH-PERFORMANCE 8 X 8 BOOTH        |    |

| MULTIPLIER WITH PARALLEL ADDITIONS IN [41]                                    | 34 |

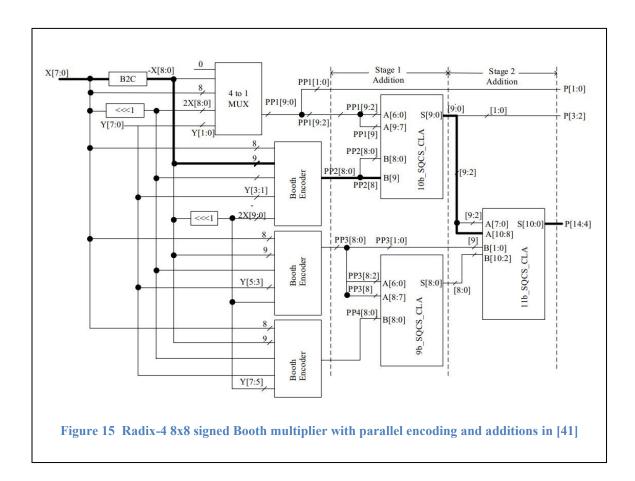

| FIGURE 15 RADIX-4 8x8 SIGNED BOOTH MULTIPLIER WITH PARALLEL ENCODING AND      |    |

| ADDITIONS IN [41]                                                             | 35 |

| FIGURE 16 LAYOUT OF THE MODIFIED RADIX-4 8x8 SIGNED BOOTH MULTIPLIER WITH     |    |

| PARALLEL ENCODING AND ADDITIONS [41]                                          | 36 |

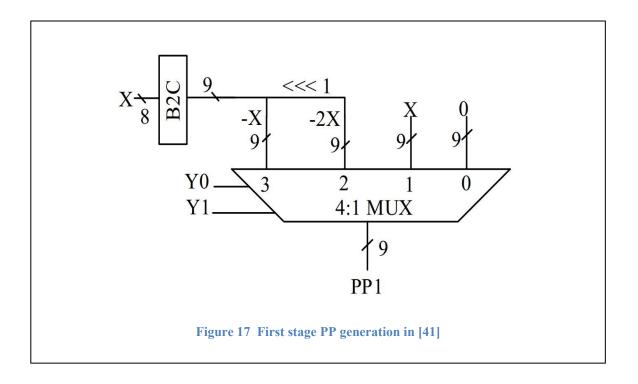

| FIGURE 17 FIRST STAGE PP GENERATION IN [41]                                           | 38 |

|---------------------------------------------------------------------------------------|----|

| FIGURE 18 (A) BOOTH ENCODER IN [43] [42], (B) OPTIMIZED BOOTH ENCODER IN [41]         | 39 |

| FIGURE 19 (A) 2ND, 3RD, AND 4TH PP GENERATION IN [41], (B) PP GENERATION IN [43] [42] |    |

|                                                                                       | 41 |

| Figure 20 Optimized radix-4 signed 8 x 8 Booth multiplier with two-stage              |    |

| ARCHITECTURE IN [41]                                                                  | 43 |

| FIGURE 21 (A) 9-BIT SQRT CS-CLA, (B) 10-BIT SQRT CS-CLA, (C) 11-BIT SQRT CS-          |    |

| CLA [41]                                                                              | 44 |

| FIGURE 22. (A) OPTIMIZED B2C USING BUBBLE PUSHING IN [42], (B) BETTER OPTIMIZED       |    |

| B2C IN [41]                                                                           | 46 |

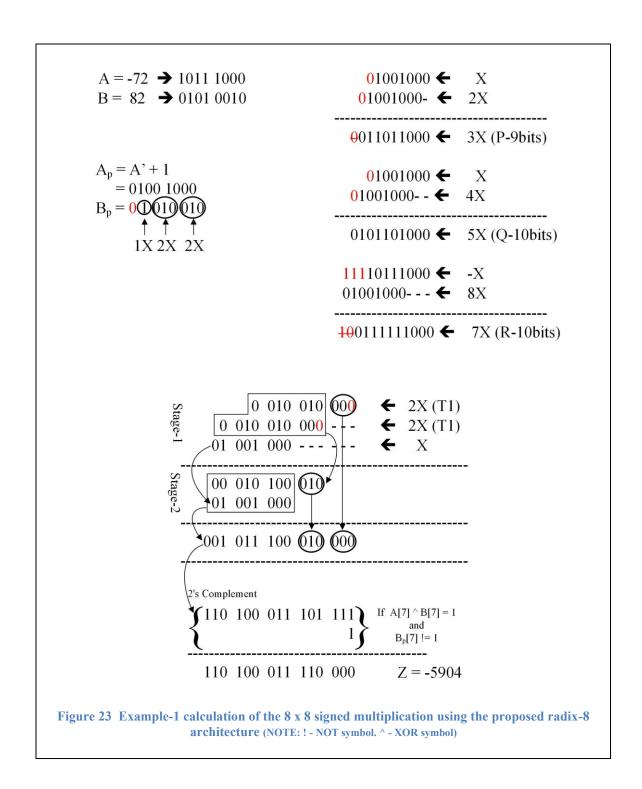

| FIGURE 23 EXAMPLE-1 CALCULATION OF THE 8 X 8 SIGNED MULTIPLICATION USING THE          |    |

| PROPOSED RADIX-8 ARCHITECTURE                                                         | 51 |

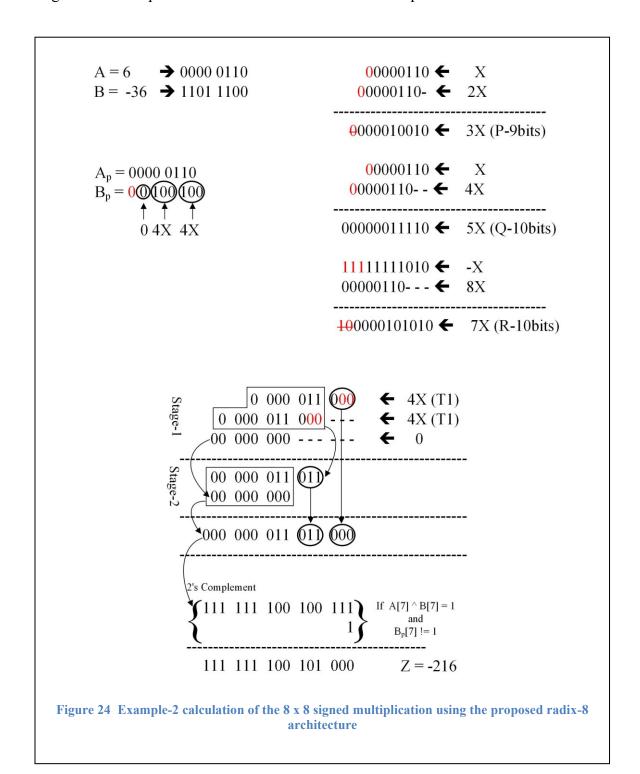

| FIGURE 24 EXAMPLE-2 CALCULATION OF THE 8 X 8 SIGNED MULTIPLICATION USING THE          |    |

| PROPOSED RADIX-8 ARCHITECTURE                                                         | 53 |

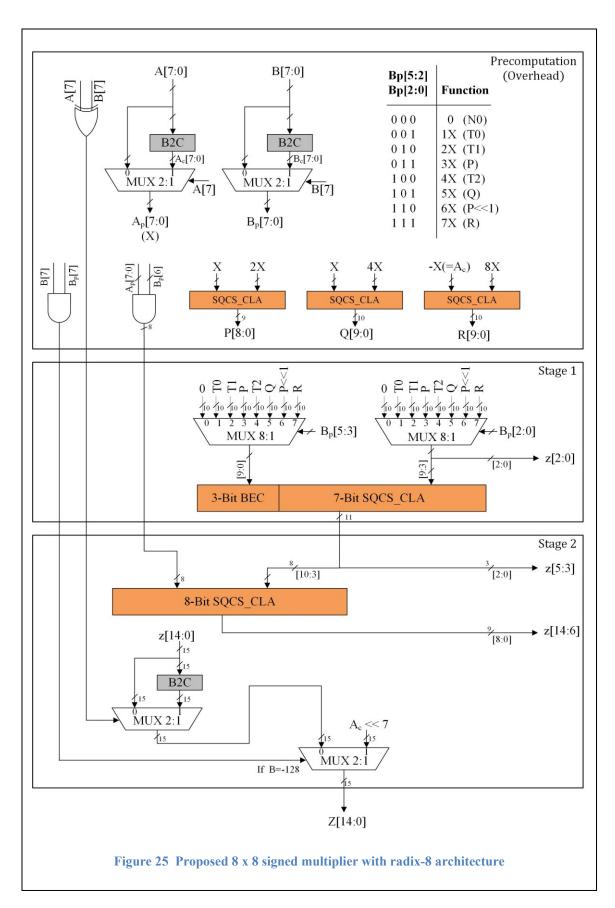

| Figure 25 Proposed 8 x 8 signed multiplier with radix-8 architecture                  | 55 |

| FIGURE 26 LAYOUT OF THE PROPOSED 8 X 8 MULTIPLIER                                     | 58 |

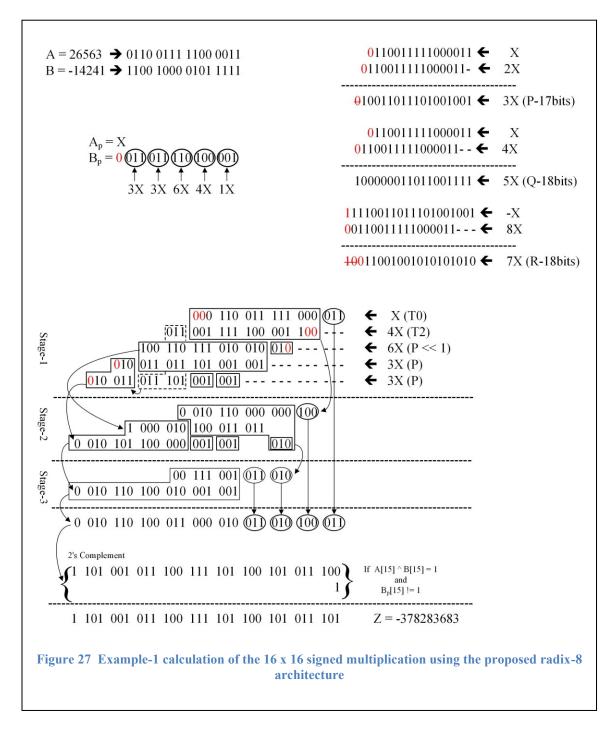

| FIGURE 27 EXAMPLE-1 CALCULATION OF THE 16 X 16 SIGNED MULTIPLICATION USING THE        |    |

| PROPOSED RADIX-8 ARCHITECTURE                                                         | 60 |

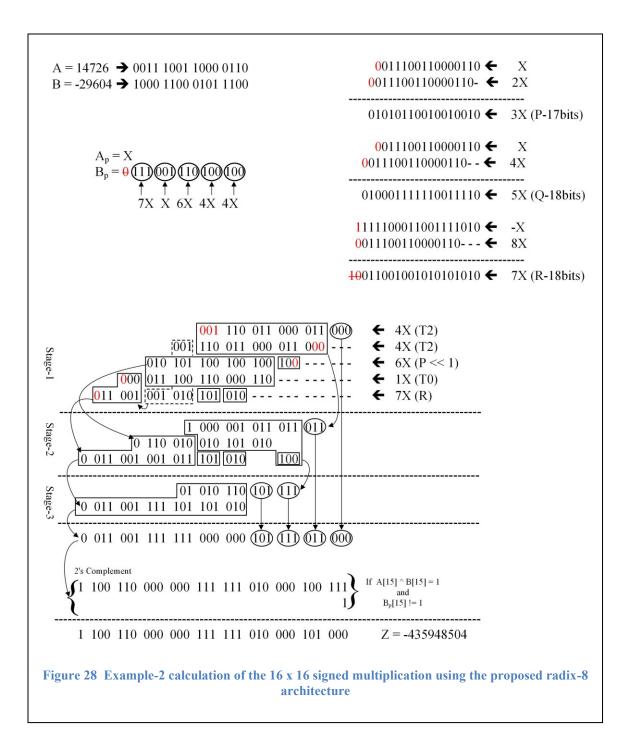

| FIGURE 28 EXAMPLE-2 CALCULATION OF THE 16 X 16 SIGNED MULTIPLICATION USING THE        |    |

| PROPOSED RADIX-8 ARCHITECTURE                                                         | 63 |

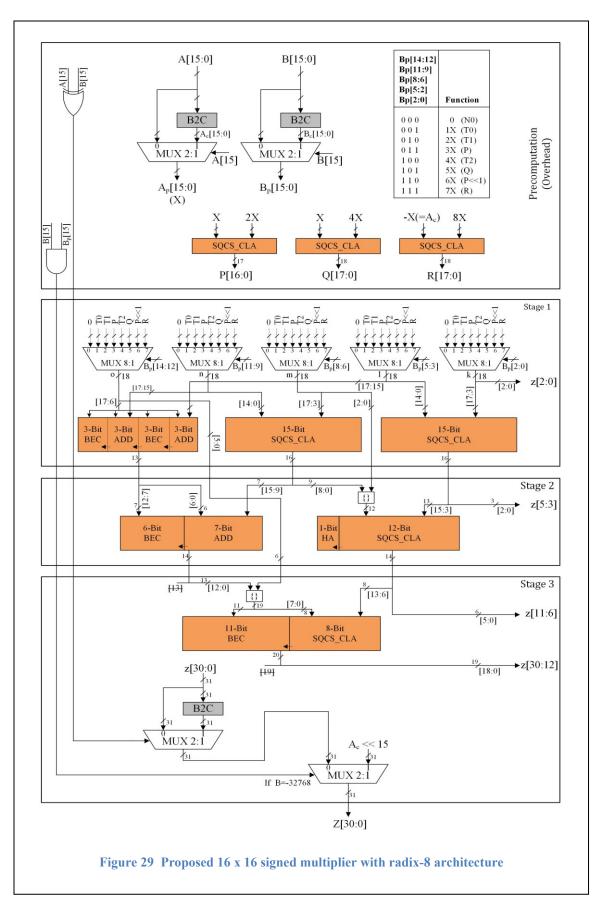

| Figure 29 Proposed 16 x 16 signed multiplier with radix-8 architecture                | 66 |

| Figure 30 Layout of the proposed 16 x 16 multiplier                                   |    |

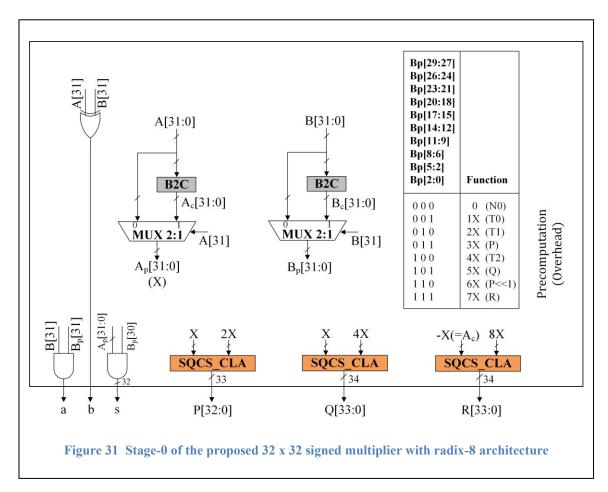

| FIGURE 31 STAGE-0 OF THE PROPOSED 32 X 32 SIGNED MULTIPLIER WITH RADIX-8              |     |

|---------------------------------------------------------------------------------------|-----|

| ARCHITECTURE                                                                          | 70  |

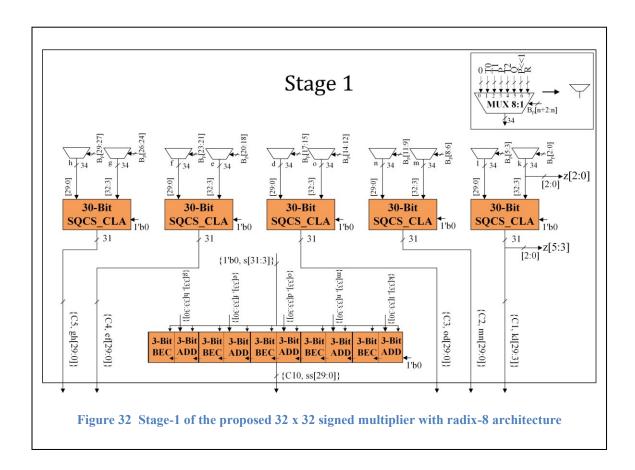

| FIGURE 32 STAGE-1 OF THE PROPOSED 32 X 32 SIGNED MULTIPLIER WITH RADIX-8              |     |

| ARCHITECTURE                                                                          | 71  |

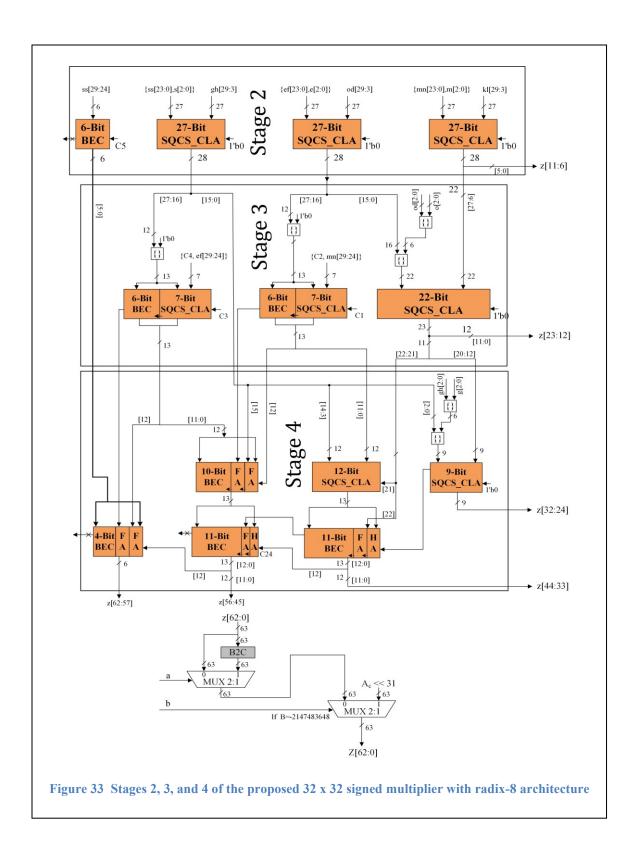

| FIGURE 33 STAGES 2, 3, AND 4 OF THE PROPOSED 32 X 32 SIGNED MULTIPLIER WITH RADIX-    |     |

| 8 ARCHITECTURE                                                                        | 73  |

| FIGURE 34 LAYOUT OF THE PROPOSED 32 X 32 MULTIPLIER                                   | 74  |

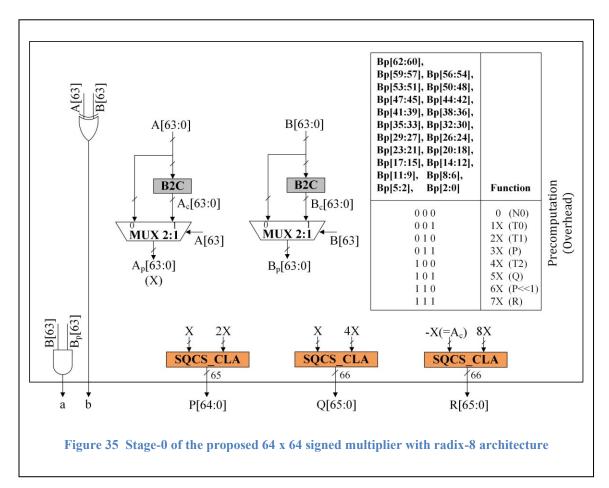

| FIGURE 35 STAGE-0 OF THE PROPOSED 64 X 64 SIGNED MULTIPLIER WITH RADIX-8              |     |

| ARCHITECTURE                                                                          | 75  |

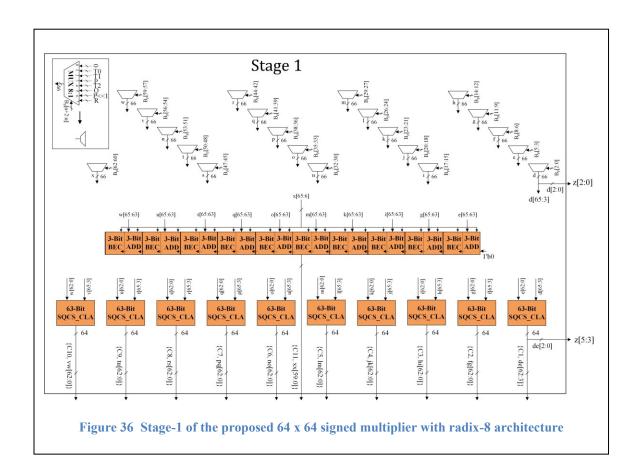

| FIGURE 36 STAGE-1 OF THE PROPOSED 64 X 64 SIGNED MULTIPLIER WITH RADIX-8              |     |

| ARCHITECTURE                                                                          | 76  |

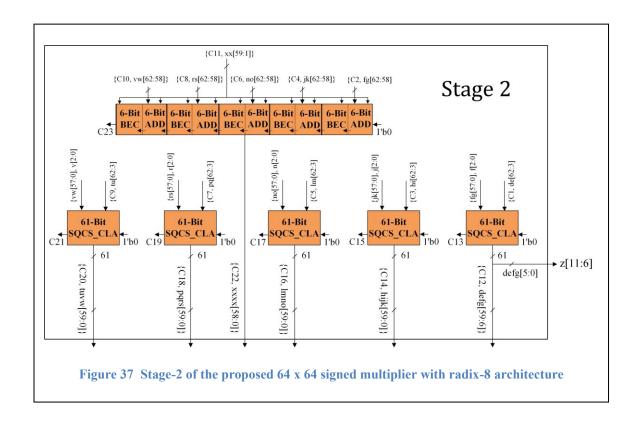

| FIGURE 37 STAGE-2 OF THE PROPOSED 64 X 64 SIGNED MULTIPLIER WITH RADIX-8              |     |

| ARCHITECTURE                                                                          | 77  |

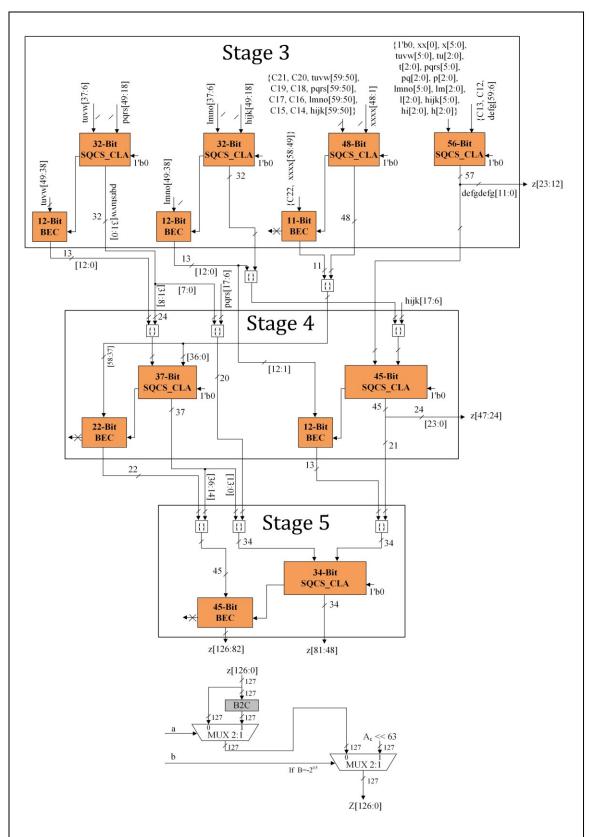

| FIGURE 38 STAGES 3, 4, AND 5 OF THE PROPOSED 64 X 64 SIGNED MULTIPLIER WITH RADIX-    |     |

| 8 ARCHITECTURE                                                                        | 79  |

| FIGURE 39 LAYOUT OF THE PROPOSED 64 X 64 MULTIPLIER                                   | 80  |

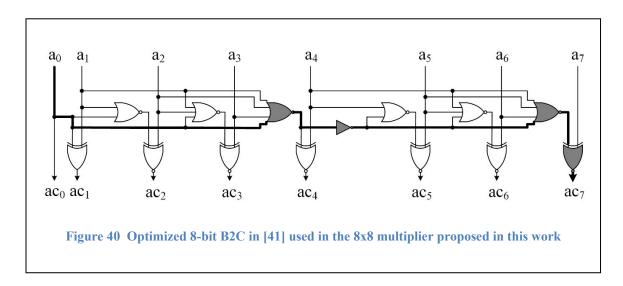

| Figure 40 Optimized 8-bit B2C in [15] used in the $8x8$ multiplier proposed in this   |     |

| WORK                                                                                  | 83  |

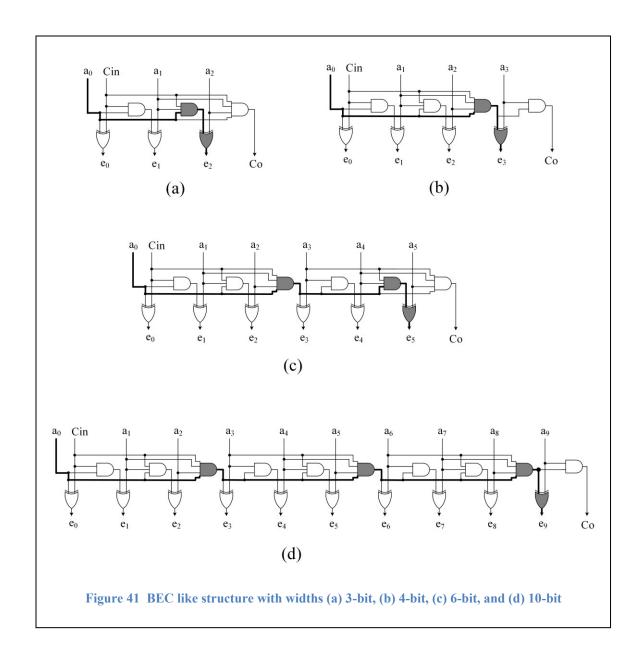

| FIGURE 41 BEC LIKE STRUCTURE WITH WIDTHS (A) 3-BIT, (B) 4-BIT, (C) 6-BIT, AND (D) 10- |     |

| DIT                                                                                   | 8/1 |

## LIST OF TABLES

| TABLE 2.1. DELAY AND COMPLEXITY COMPARISONS FOR VARIOUS SIZES OF DADDA AND                                   |    |

|--------------------------------------------------------------------------------------------------------------|----|

| WALLACE MULTIPLIERS WITH RCA AND CLA PRESENTED IN [8]                                                        | 19 |

| TABLE 2.2 RADIX-4 BOOTH ENCODING SCHEME [4]                                                                  | 21 |

| TABLE 3.1 FIRST STAGE ENCODING SCHEME [41]                                                                   | 37 |

| TABLE 3.2 COMPARISON OF THE SYNTHESIS (PRE-LAYOUT) RESULTS FOR THE B2C DESIGNS                               |    |

| [41]                                                                                                         | 47 |

| TABLE 4.1 BOOTH MULTIPLIER WITH BINARY TREE STYLE REDUCTION OF PARTIAL                                       |    |

| PRODUCTS USING ADDERS                                                                                        | 48 |

| TABLE 4.2 PROPOSED RADIX-8 (3-BIT) GROUPING TO SEPARATE TRIVIAL AND NON-TRIVIAL                              |    |

| COMPUTATIONS                                                                                                 | 49 |

| TABLE 4.3 SYNTHESIS (PRE-LAYOUT) RESULTS FOR 8-BIT AND 16-BIT B2C IN [41]                                    | 82 |

| Table 4.4 Synthesis (pre-layout) results for the sub-components used in the $8\ \mathrm{x}$                  |    |

| $8, 16 \times 16, 32 \times 32, \text{ and } 64 \times 64 \text{ signed multiplier designs proposed } \dots$ | 86 |

| TABLE 4.5 SYNTHESIS AND POST-LAYOUT RESULTS FOR THE PROPOSED DESIGN                                          | 90 |

| TABLE 4.6 SYNTHESIS AND POST-LAYOUT RESULTS FOR THE PROPOSED DESIGNS                                         |    |

| SYNTHESIZED AT HIGHEST FREQUENCY                                                                             | 92 |

| TABLE 4.7 COMPARISON OF TOTAL DYNAMIC POWER (TDP) AND CELL LEAKAGE POWER                                     |    |

| (CLP) FOR THE PROPOSED SYNTHESIZED AND POST-LAYOUT DESIGNS OF VARIOUS                                        |    |

| SIZES                                                                                                        | 94 |

| TABLE 4.8 PERFORMANCE COMPARISON OF THE MULTIPLIERS                                                          | 96 |

#### **Acknowledgements**

First and foremost, I would like to acknowledge and thank my dissertation advisor and dissertation committee chair Dr. Saiyu Ren. I would also like to especially thank Dr. Saiyu Ren for understanding, supporting, and encouraging my strong desire for an independent and broad range of study/research. Thanks to be with me for the last 9+ years, since the beginning of my first master's career at Wright State University, for listening to my ideas, for the initial years of support and encouragement towards my teaching career, for appreciating and expressing exciting views on my teaching and research at various occasions, and for spending time on reviewing my work, documents, and articles and providing the feedback. I would also like to thank my dissertation committee members, Dr. Ray Siferd, Dr. Henry Chen, Dr. Marian K. Kazimierczuk, and Dr. Yan Zhuang, and the external observer, Dr. Tarun Goswami, for spending their valuable time and effort to review my work and provide feedback.

I would like to thank all the faculty members, Dr. Saiyu Ren, Dr. Ray Siferd, Dr. John Marty Emmert, Dr. Henry Chen, and Dr. LaVern A. Starman, who taught VLSI-related subjects in my master's in Electrical Engineering career. I would also like to thank all the faculty members, Dr. Jack S. Jean, Dr, Pradeep Misra, Dr. Ronald Taylor, Dr. Yan Zhuang, Instructor Dennis Hance, Dr. Yong Pei, Dr. John Nehrbass, Dr. Nikolaos G. Bourbakis, and Dr. Jeff Clark, who taught other subjects in my student career, Ph.D. in EE and second masters in CEG.

I would like to especially thank Dr. Raymond E. Siferd for the encouragement provided and I always keep in mind the valuable suggestions. I would also like to especially thank Dr. Marian K. Kazimierczuk for sharing some of his life experiences, achievements, and suggestions related to studies and research, which I keep in mind forever.

A special thanks to a very important person, Mike VanHorn (Senior Computer Systems Administrator) in my student, teaching, and research career. I cannot express in words how thankful I am to Mike (a very knowledgeable, humble, great human being, and an invaluable asset to WSU) for the last 9+ years of continuous help and support on numerous occasions in fixing any hardware and software-related issues. I would like to thank Simon A. (Tony) Tritschler, laboratory manager, for the help he provided me being a lab instructor and a research student.

I would like to thank the EE department chairs, Dr. Kefu Xue (before 2014) and Dr. Brian D. Rigling (2014-2017), and the current dean of the CECS, Dr. Brian D. Rigling. I would also like to thank especially the EE department staff, including academic advisors, Dr. Ryan Hamilton, Lori Luckner, Vickie Slone, Nickey Brown, Elizabeth Anne Generas, and Amanda Ellen Steward. A special thanks to Vickie Slone and Amanda Ellen Steward for their help in the final semesters of teaching and completion of the dissertation. I

would also like to thank the other staff members at Wright State University, Donna J. Harris, Kimberly Ann Brumbaugh (DSO), Gwana Snell, Scott, and many others for their help. I would like to thank Erika Gilles (Associate Director of Academic Affairs, Graduate School) for the assistance provided at various occasions and for performing the format check of this dissertation document.

Thanks to all the faculty members, Dr. Henry Chen, Dr. Saiyu Ren, Dr. John M. Emmert, Instructor Dennis Hance, Dr. Gorman, Dr. Kefu Xue, Dr. Mike Saville, Dr. Pradeep Misra, Dr. Robert Allen Myers, and Dr. Marian K. Kazimierczuk, for whom I taught the labs for, for the trust, support, and appreciation. A very special thanks to my students whom I taught labs/classes for. Thanks for the cooperation provided in the lab, for making my teaching career so exciting and enjoyable, and for the love and appreciation. I will cherish the memories, accumulated over the years, forever.

Finally, I would like to thank all my family members for the unparalleled love and immense support. And, I would like to also thank the friends and well-wishers who were/are/will be always loving me and being with me.

#### 1 Introduction

#### 1.1 Digital Multiplier

Addition and Multiplication are the most often used elemental components of digital computing devices such as DSP, microprocessor, etc. Multiplier is the most used computer arithmetic after addition and subtraction. DSPs use multipliers for frequently used computationally intensive applications such as filtering: finite impulse response (FIR) filter, infinite impulse response (IIR) filter, and adaptive filters of types of least mean squares (LMS) filter and recursive least mean squares (RLS) filter; convolution: linear and circular convolution, Fast Fourier Transform (FFT), audio/video codecs etc. High performance computer hardware, CPUs, and GPUs, for scientific computing rely majorly on use of these fundamental digital arithmetic. Digital signal processors spend most of the time multiplying and requires more chip area of multipliers to meet the performance requirements. Multipliers often contributes towards critical path delay which in turn effects the throughput in case of pipelined designs and consumes more power in applications such as multimedia and DSP. Demand for low power consuming portable computing and communication devices such as smart watches, IoT devices, mobile phones, laptops, PCs etc., comprise of signal processing algorithms and other multiplication intense algorithms, has been increasing. Specifically, the global market for wireless portable medical devices is going to see a huge growth in next five years. According to the market research report [1], "The Global Portable Medical Devices

Market is estimated to be USD 38.1 Bn in 2021 and is expected to reach USD 68.24 Bn by 2027, growing at a CAGR of 10.2%.", and according the report [2], "Global portable medical devices market will reach \$99.89 billion by 2030, growing by 9.8% annually over 2020-2030 owing to the rise in demand for portable medical devices, increase in geriatric population, growing incidences of chronic diseases, increasing government support, rising R&D investment and technological advancement.". "The global wearable medical devices market size was valued at USD 16.6 billion in 2020. It is expected to expand at a compound annual growth rate (CAGR) of 26.8% from 2021 to 2028. The growth of industries such as home healthcare and remote patient monitoring devices is anticipated to influence market growth. In addition, increasing focus on fitness and a healthy lifestyle orientation are also expected to impact the market." [3] with the revenue forecast in 2028 as USD 111.9 billion. The importance of need for inventing multiplier algorithms is supported by the statement "At least one good reason for studying multiplication and division is that there is an infinite number of ways of performing these operations and hence there is an infinite number of PhDs (or expensespaid visits to conferences in the USA) to be won from inventing new forms of multiplier." by Alan Clements in the year 1986.

#### 1.2 Research motivation and objective

As the usage of the digital hardware is getting increased, digital hardware become ubiquitous and a part of the gadgets, appliances, or vehicles used by and for human. With the advancements in chip manufacturing technologies such as 10nm, 7nm, and 5nm nodes, the density of the transistors is increasing and hence the power dissipation. The chip manufacturing technologies are getting matured, and the node sizes are tending to

approach the atomic sizes. With billions of people using multiple digital devices and a huge number of digital devices deployed, for the direct use or for the indirect use, for the people, and the advancements of new technologies such as digital health, Inter-of-Things (IOTs), etc., the demand for the digital devices with a combination of one or more performance attributes and cost attributes such as low-area, low-power, and high-speed has been increasing. Low-power digital designs are in great demand for biomedical signal processing. This work focuses on finding the solutions for low-cost and high-speed designs at algorithmic level instead of exploring for an advanced node technology.

The objective of this work is to designing low-power, low-cost, and high-speed signed integer multipliers. The research is started with the best algorithm, Booth algorithm, for the signed number multiplication either to optimize the existing algorithm or to find new architectures. The objective includes designing the optimized algorithms using 32nm CMOS technology, performing synthesis, generating the post-layout, and comparing the performance of the modified or proposed designs with the state-of-the-art designs.

#### 2 Literature Review

#### 2.1 Digital Multiplier

This and the following subsection of this chapter presents the summary of the literature study on multipliers with an emphasis on signed Booth multiplier algorithms. An extensive work on optimization of multiplication circuits has been performed [4], [5] and is continuing. Standard binary multiplication uses repeated shift and accumulate routine. Therefore, the mechanisms to improve the multiplier speed involves dealing with the combination of the following process: partial product generation (PPG) & Partial product reduction (PPR), and acceleration of the accumulation of the shifted partial products (PP). Smaller number of PPs require lesser number of resources to build and hence reduces the design complexity, design area, and time & power required for the accumulation process, i.e., minimization of power-delay product (PDP) and power-delayarea (PDA) product which is also known as energy-area product (EAP). According to [5], study of various implementations of shift/add multiplications leads to a conclusion to come up with two ways to improve the speed of intrinsic multi-operand addition: high radix multipliers to reduce the number of operands to be added, and tree and array multipliers to compose multi-operand adders to minimize latency and/or maximize the throughput.

The following notation adapted from [5] is used in this discussion of multiplication algorithms:

$$X$$

Multiplicand  $x_{n-1}x_{n-2} \dots x_1x_0$  (2.1)

$$Y$$

Multiplier  $y_{n-1}y_{n-2} \dots y_1y_0$

P Product

$$(x \times y)$$

$p_{2n-1}p_{2n-2} \dots p_1p_0$

(2.2)

(2.3)

#### 2.2 Multiplier Architectures

Various binary multiplier architectures such as array and tree multipliers for unsigned multiplication and the optimized booth algorithms for signed multiplication are discussed in this section.

#### 2.2.1 Array Multiplier

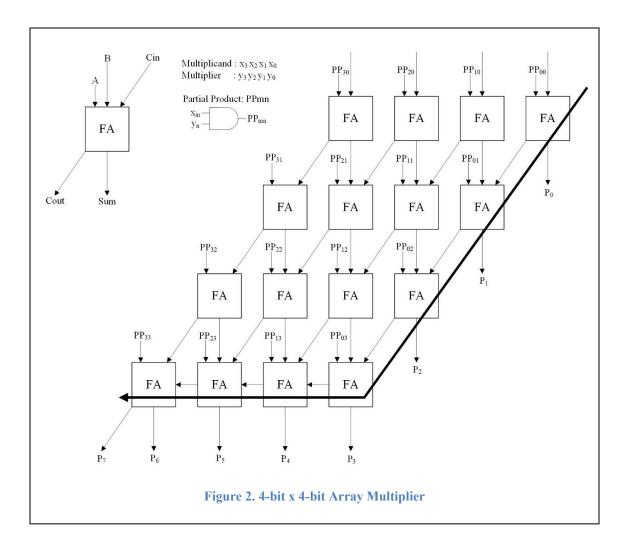

An array multiplier is a combinational circuit in the shape of parallelogram used for multiplying two binary numbers, multiplicand (x) and multiplier (y), by using an array of full adders (FA) and half adders (HA) employed in simultaneous addition of the product terms generated by an array of AND gates. An example of binary multiplication is shown in Figure 1.

An array multiplier has a simple structure and is designed by placing the FA and HA blocks horizontally, row-wise, and vertically, column-wise. Hence, the structure is more compatible to modify to pipeline structure, smaller, and requires less design time. Rows of PPs and adders are treated as stages. All stages work parallelly by processing the respective partial products before each adder while carry-out propagating to the next row. Critical path is the limiting factor in non-pipelined structure to achieve high speed or throughput. As highlighted in Figure 2 with bold line, critical path has vertical and horizontal parts with similar delay contributions in both directions by the gate delays and adder delays. The worst-case delay of the structure is proportional to the width of the multiplier i.e., for an n-bit by n-bit array multiplier the delay is nearly equal to the two times the number of full adders in a row or a slanted column. Hence, the width of an array multiplier limits the speed.

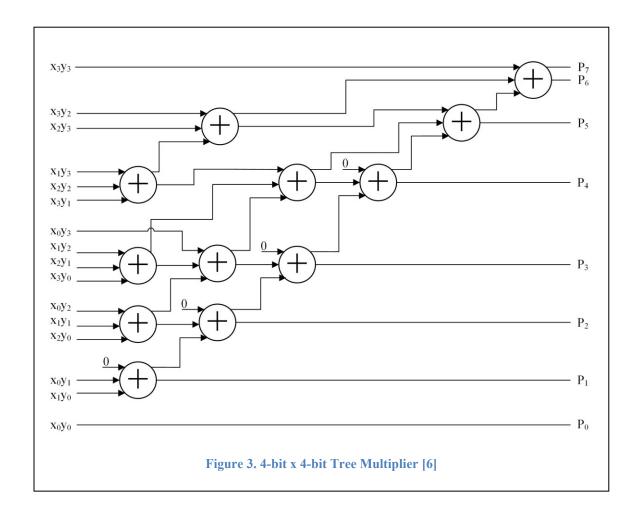

#### 2.2.2 Tree Multiplier [6]

Unlike the generation of PPs and accumulating the PPs in a regular array multiplier, tree structure shown in Figure 3 deploys number of full adders, each one as a 3:2 compressor, to reduce the three input bits to two output bits: sum bit and carry out bit. A full adder acts like a compressor or as an encoder by converting three binary inputs to two encoded binary output with a compression factor of 1.5. The advantage of employing the 3:2 compressors in the tree structure is that it does not involve longer carry propagation along multiple stages and hence this process is faster than the conventional way of multiplication. Summands are grouped in each step to reduce, and the process of

grouping and compression continues until only two numbers remain. Total time of adding to the last step is proportional to the logarithm of the number of summands.

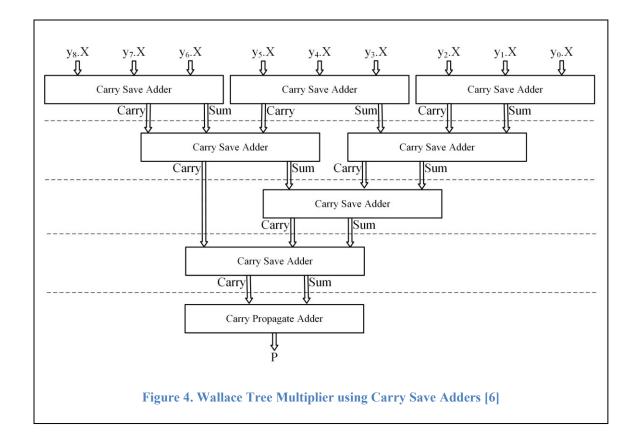

#### 2.2.2.1 Wallace Tree Multiplier (WTM) [7]

Wallace tree structure using carry-save adders to sum the multiplicand-multiples in parallel is shown in Figure 4. A carry save adder takes three binary inputs and yields two binary outputs. The advantage of the Wallace tree multiplier is its tree like structure with the carry save adders which ensures less delay due to the reduced number of logic levels. The disadvantage of this structure is its complex structure to design the layout and very high hardware requirement.

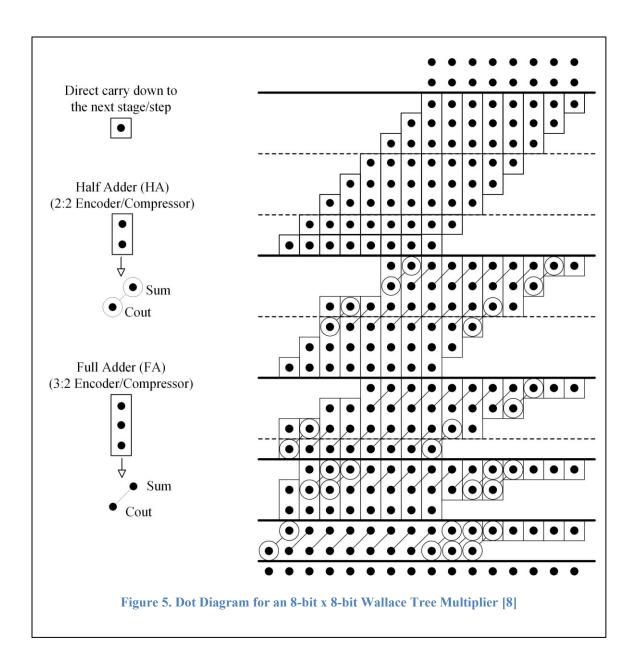

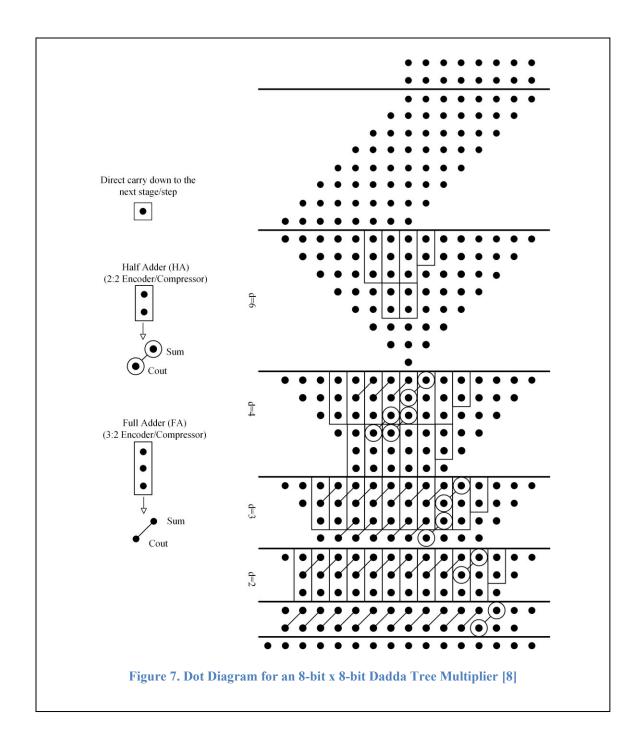

The essential feature of Wallace tree architecture is to find the final product using least number of possible steps. Hence, at each step maximum number of bits, shown as solid dots in [8], are covered in each step vertically to compress using half adder to encode two bits and full adder to encode three bits. This process is illustrated in Figure 5. Any bits uncovered, groups of two or three, are transferred to the next stage without any further processing. As mentioned earlier, half adder acts like a 2:2 compressor and full adder like a 3:2 compressor. The steps are continued until only two or a smaller number of bits remaining at each bit position at the end of the completion of a step. All the compressions are carried out in parallel at each step. At each step, the lone bit on the least significant bit (LSB) positions or on the most significant bit (MSB) positions are transferred down to the next step without any processing.

Sum and carry out output bits obtained from the full adder in the current step are depicted using a diagonal line joining two solid dots in the next stage. Similarly, the two output bits of the half adder are shown in the next stage using an inclined solid line of joining two circles enclosing the respective bit of a partial product, solid dot. Recursive equations used to determine the height of the  $j^{th}$  reduction stage,  $\omega_j$ , where j starts from 0, are shown below [9] using equations (2.4) and (2.5).

$$\omega_0 = N$$

$\omega_{j+1} = 2 \cdot \left\lfloor \frac{\omega_j}{3} \right\rfloor + \omega_j \mod 3$

(2.5)

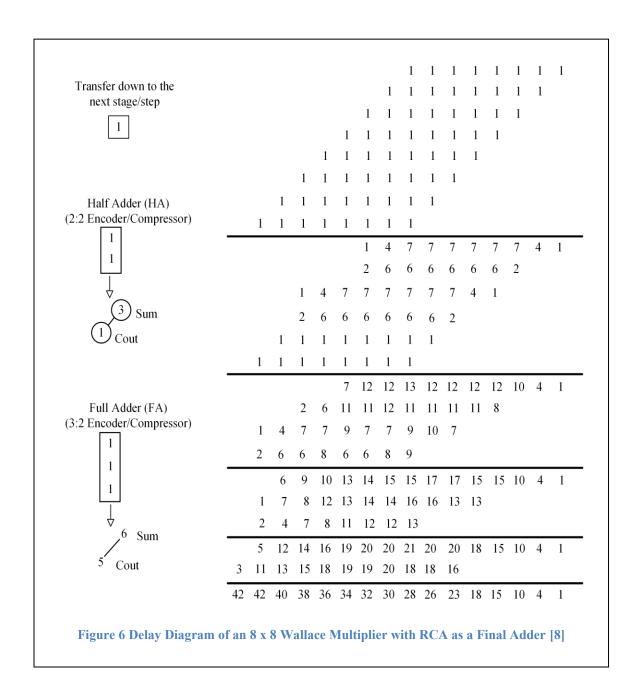

In the dot diagram shown in Figure 5 for an 8 x 8 Wallace multiplier, four reduction stages can be observed with heights of 6, 4, 3, and 2 respectively. And, the total digital hardware required for the multiplication includes 64 AND gates, 1 OR gate, 38 3:2 compressors, 15 2:2 compressors, and 10-bit carry propagation adder (CPA). The number of 2:2 compressors required are either equal or greater than N and often much greater than N. Given the number of bits of operands, N, and calculating the number of stages of reduction to reduce the PP matrix from N-rows to 2-rows, S, the number of 3:2 compressors and the size of the final CPA adder can be determined by the following criteria [10] shown using equations (2.6) to (2.10).

$$3 \le N \le 5$$

$$(3,2) \text{ counters} = N^2 - 4 \cdot N + 3 + S$$

$$(2.6)$$

CPA length =  $2 \cdot N - 2 - S$

(2.7)

5 < N

(3,2) counters =

$$N^2 - 4 \cdot N + 2 + S$$

(2.8)

or

(3,2) counters =

$$N^2 - 4 \cdot N + 1 + S$$

(2.9)

CPA length =  $2 \cdot N - 1 - S$  (2.10)

Discussing about the delay estimation, all  $N^2$  partial products are generated in parallel by exercising the bit-by-bit multiplication using a simple two input AND gate. Hence, the delay contributed by PP generation is of O(1) complexity. Delay estimation for the Wallace multiplier is performed in [8] considering a nine gate full adder, comprised of only 2-input AND, 2-input OR, and inverter gates, as 3:2 compressor and a half adder, comprised of four 2-input gates, as 2:2 compressor while considering that all the two input standard cells having nearly equivalent area, gate count, and a delay of 1. Assuming the simultaneous arrival of all the input signals to the compressors, the delays of the sum, LSB output bit, and carry out, MSB output bit, signals for the full adder as 3:2 compressor are 6 gate delays and 5 delays respectively, and the delays of sum and carry-out output signals of the half adder, as 2:2 compressor, are 3 and 1 gate delays respectively. Similarly, the delay estimation for the Dadda tree multiplier discussed in the following sub-section relies on the gate count and delay consideration made above. The following delay diagram for an 8 by 8 Wallace multiplier with an RCA as final adder is presented in [8], shown in Figure 6, with detailed explanation.

A low power and scalable counter-based modular Wallace tree (CBMW) multiplier is presented in [11]. Partial products are reduced using a power efficient sequential 7:3 counter, composed of multiplexer and XOR, and by applying multibit addition in a single column. Power consumption is reduced by deploying a single 7:3 counter to perform the partial product reduction in each column. Only a single 7:3 counter used per each stage of partial product reduction applying inputs serially. 7:3 counter presented in [12], which is an efficient 7:3 counter than the ones presented in [13], [14], [15], and [16], is used. The performance of the CBMW multiplier is compared

in terms of power, delay, total cell area, and PDP against the other variants such as conventional WTM, Reduced Complexity Wallace (RCW) tree multiplier [17], Counter-Based Wallace (CBW) tree multiplier [18] [16], etc.,.

Ever increasing use of the Booth-encoding in reduction of number of partial products led to the work in [19] to perform the performance comparison between RCW multiplier and radix-4 Booth-Reduced Complexity Wallace (R4B-RCW) multiplier and the synthesis results clearly show that the RCW performs significantly better than the R4B-RCW multiplier in terms of both speed and power consumption.

#### 2.2.2.2 Dadda Tree Multiplier [20]

Dadda tree binary multiplier design is an optimized scheme invented by computer scientist, Luigi Dadda, in 1965 to compute the multiplication of the unsigned fixed-point numbers. Like Wallace tree structure, Dadda tree multiplier is also a column compression multiplier consists of three stages: Partial product matrix formation in stage 1, reduction of partial product matrix height to 2 in stage 2, and accumulation of these final two rows using carry propagation adder in the final stage.

Dadda tree multiplier has same number of reduction levels as Wallace tree multiplier with variation of matrix height at different levels. The number of full adders in both the tree structures is nearly the same. However, Wallace adder uses more of the full adders and a greater number of half adders in the reduction levels leading to a shorter

final CPA adder compared to the Dadda multiplier. Dadda multiplier use a minimal number of compressors in each level of compression to achieve the required compression and the recursive reduction procedure is as follows [21] [8]:

- 1. Starting from  $d_1=2$  as the final stage of reduction and N as the height of the original PP matrix, calculate  $d_j$ , the height of the matrix at  $j^{th}$  level of reduction from the bottom, using  $d_j=\left\lfloor \frac{3}{2}\cdot d_{j-1}\right\rfloor$ . Repeat calculating the  $d_j$  until reaching the largest matrix of at  $j^{th}$  level where  $d_j< N< d_{j+1}$ .

- 2. Starting from the highest  $j^{th}$  stage from the end, matrix in each stage needed to be reduced using (3,2) and (2,2) counters to the desired heights calculated in the previous step. Reduction should be performed on only columns with dots greater than the required stage height,  $d_j$ . Carries coming from the least significant (3,2) and (2,2) counters are needed to consider as dots while reducing.

- 3. Repeat the reduction procedure in step two on each stage until reaching the final stage of height  $d_1=2$ .

The dot diagram for 8 by 8 Dadda multiplier is shown in Figure 7. All three stages involving PP matrix generation, matrix reduction, and final CPA additions are shown in the figure. In stage 2 of reduction, each of four levels of reduction are labeled with the respective matrix height reduction requirement as 6, 4, 3, and 2 from the top to the bottom level. Digital hardware required to build the Dadda multiplier includes 64 AND gates in the first stage, 35 3:2 compressors and 7 2:2 compressors in the second stage, and

a 14-bit CPA adder in the final stage. Given N as the number of bits of operands, the number of (3,2) counters, (2,2) counters, and the size of the final CPA adder are determined as follows:

(3,2) counters =

$$N^2 - 4 \cdot N + 3$$

(2.11)

$$(2,2)$$

counters =  $N-1$

(2.12)

CPA length =

$$2 \cdot N - 2$$

(2.13)

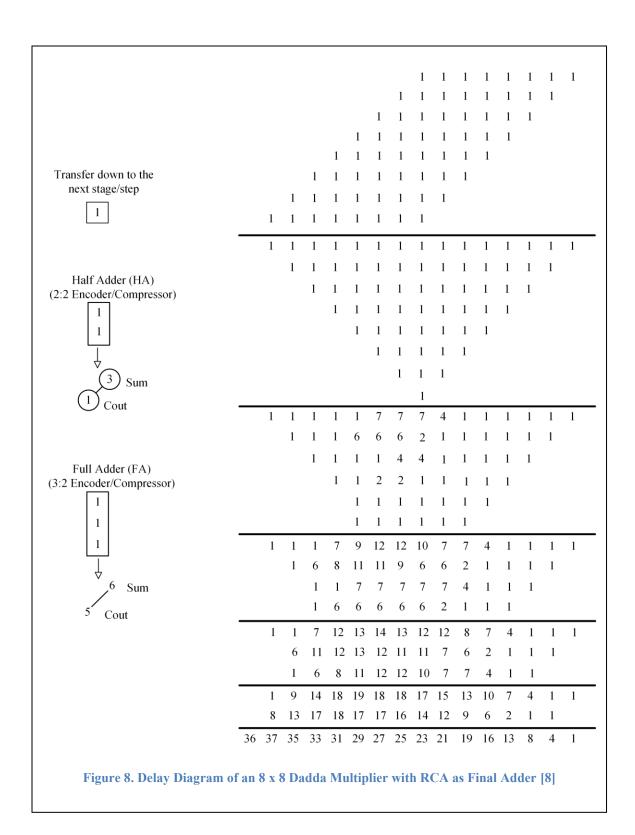

The article [8], includes the discussion of delay estimation methodology, concluded about the delay comparison based on the closed examination performed between Dadda and Wallace multipliers that the general assumption of slightly faster response of Wallace multiplier due to the smaller final stage adder is incorrect. The delay calculation diagram is depicted in Figure 8 and the results presented in [8] by performing detailed analysis on both tree structures varying the operand sizes with both RCA and CLA are shown in Table 2.1 and concluded that the delay and complexity of Dadda multiplier is less compared to Wallace multiplier.

Table 2.1. Delay and Complexity Comparisons for various sizes of Dadda and Wallace Multipliers with RCA and CLA presented in [8]

| <b>Multiplier Size</b> | Delay Complexity |            | plexity      |              |  |

|------------------------|------------------|------------|--------------|--------------|--|

|                        | Dadda            | Wallace    | Dadda        | Wallace      |  |

| with RCAs              |                  |            |              |              |  |

| 4 x 4                  | 19 (100%)        | 21 (111%)  | 104 (100%)   | 104 (100%)   |  |

| 8 x 8                  | 37 (100%)        | 42 (114%)  | 528 (100%)   | 552 (105%)   |  |

| 16 x 16                | 69 (100%)        | 77 (112%)  | 2336 (100%)  | 2476 (106%)  |  |

| 32 x 32                | 133 (100%)       | 145 (109%) | 9792 (100%)  | 10283 (105%) |  |

|                        | with CLAs        |            |              |              |  |

| 4 x 4                  | 15 (100%)        | 18 (120%)  | 120 (100%)   | 112 (93%)    |  |

| 8 x 8                  | 29 (100%)        | 31 (107%)  | 573 (100%)   | 582 (102%)   |  |

| 16 x 16                | 43 (100%)        | 45 (105%)  | 2440 (100%)  | 2557 (105%)  |  |

| 32 x 32                | 54 (100%)        | 56 (104%)  | 10013 (100%) | 10475 (105%) |  |

Signed Radix-2<sup>m</sup> parallel multipliers with two new sign extension techniques to improve the energy efficiency with smaller design area presented in [22] with partial product compression performed in both Wallace and Dadda styles deploying two variants, one employing RCA-less optimization (NR) and the second one employing optimized sign extension without intermediary ripple carry adders (NR-SO) for multipliers of operand widths 8, 16, 32, and 64.

An efficient signed carry-save multiplier (CSM) with modified square root carry-select adder (MSCA), instead of conventional vector-merging adder (CVMA), for the vector-merging addition and improved full adder (IFA), in place of regular full adder, is presented in [23]. 8-bit and 16-bit wide multipliers are designed, synthesized, and made comparisons with the state-of-the-art designs to show that there is a remarkable improvement in the performance metrics, critical path delay (CPD), power, PDP, area, and ADP.

#### 2.2.3 Booth Multiplier

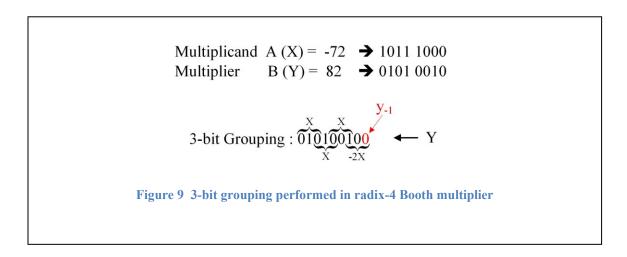

A signed multiplier technique is presented in [4] by Andrew D. Booth hence the name Booth multiplier. Booth multiplier architecture works mainly on the partial product generation using the Booth encoding scheme in Table 2.2. Though the encoding scheme looks like using three bits of the multiplier, the effective number of bits used at any stage of partial product generation are two and hence the encoding scheme is a radix-4 scheme.

The grouping, shown in Figure 10, and encoding starts from the LSB side and proceeds towards the MSB side of the multiplier. First 3-bit grouping on the LSB side includes a padded bit-0 at -1<sup>th</sup> location, a pseudo index, and the next two bits include the LSB bits at 0<sup>th</sup> and 1<sup>st</sup> bit positions of the multiplier. The second 3-bit grouping include the MSB bit of the previous 3-bit grouping as an LSB bit and the next two bits include the adjacent bit values proceeding towards the MSB side, i.e., bits at indexes 2 and 3 respectively. This grouping process continues until the end of the multiplier bits. Even number of multiplier bits result in complete grouping of all the bits. Since the effective number of bits used per group are two and the number of groups equal to half the total number of multiplier bits.

Table 2.2 Radix-4 Booth encoding scheme [4]

| $y_{2i+1}$ | y <sub>2i</sub> | $y_{2i-1}$ | Partial Product |

|------------|-----------------|------------|-----------------|

| 0          | 0               | 0          | 0               |

| 0          | 0               | 1          | +X              |

| 0          | 1               | 0          | +X              |

| 0          | 1               | 1          | +2 <i>X</i>     |

| 1          | 0               | 0          | -2X             |

| 1          | 0               | 1          | -X              |

| 1          | 1               | 0          | -X              |

| 1          | 1               | 1          | 0               |

|            |                 |            |                 |

A high-speed parallel Booth multiplier with new modified Booth encoding (MBE) scheme to achieve better performance than the traditional MBE schemes, modified PPA, and a new addition algorithm, multiple-level conditional-sum adder (MLCSMA), to perform the final addition is presented in [24]. One of the two common methods of generating partial products in the first stage is using radix-4 MBE [4] [25] which reduces the number of partial products by a factor of two. Area and delay profiles of new MBE scheme proposed is compared with several other existing MBE schemes and can be observed that the proposed scheme is faster while requiring moderate design area. Partial product reduction tree (PPRT) is used to effectively sum up all the partial products generated. Also, examined and concluded that the parallel multiplier constructed using Three-Dimensional-reduction-Method (TDM) [26] [27] with MBE is faster with smaller area. Partial product reduction using 4:2 compressor is faster compared to using Wallace

tree and Carry-save tree which uses 3:2 compressor, full adder, as a basic element, whereas, the TDM outperforms the 4:2 compressor in speed. New MLCSMA presented and used is constructed using conditional-sum adder (CSMA) and the conditional-carry adder (CCA) and showed an improvement of up to 25% performing final addition when designed in 350nm technology at supply voltage of 3.3 V. Since the tree based CSMA is a very regular structure with the performance compared to CLA adder. The hybrid adder structure retains the speed from by using the conventional CSMA [28] and saves area using CCA [29].

Modified Booth algorithms performing speed critical wide operand multiplications with very high radix structure accompanied by deployment of reduced area adder trees is presented in [30] resulting in large increase in speed with reasonable design area. Another modified Booth algorithm with optimized radix-4 Booth encoders for partial product generation and effective use of (3,2), (5,3), and (7,4) compressors for partial product reduction in vertical direction is presented in [31].

#### 2.2.4 Baugh-Wooley Two's Complement Signed Multiplier [32]

A high-speed two's complement m-bit by n-bit parallel array multiplier for signed multiplication, also known as Baugh-Wooley multiplier, is presented in 1973 [32] with the focus on the solving the problems caused by the sign bits in signed number multiplication using the most common two's complement representation. Conventional two's complement multiplier contains partial products with both the positive and negative signs. However, the Baugh-Wooley multiplier has an advantage over the conventional two's complement multiplier is that the signs of all the partial product bits are positive. Conventional two's complement binary multiplication, shown in Figure 10, multiplies the

multiplicand  $X = (x_{m-1}x_{m-2} \dots x_1x_0)$  with multiplier  $Y = (y_{n-1}y_{n-2} \dots x_1x_0)$  resulting in the m+n bit product  $P = (p_{m+n-1}p_{m+n-2} \dots p_1p_0)$ . Product is the result of the sum of the partial product bits formed by AND each of the multiplicand bit with the multiplier bit.

Let the values of the X and Y be  $X_v$  and  $Y_v$  which are given by the following equations (2.14) and (2.15) included in [32].

$$X_{v} = -x_{m-1}2^{m-1} + \sum_{i=0}^{m-2} x_{i}2^{i}$$

$$Y_{v} = -y_{n-1}2^{n-1} + \sum_{j=0}^{n-2} y_{j}2^{j}$$

(2.14)

(2.15)

Let the value of the product P be  $P_v$ , and is represented by the equation (2.16).

$$P_{v} = -p_{m+n-1}2^{m+n-1} + \sum_{i=0}^{m+n-2} p_{i}2^{i} = X_{v}Y_{v}$$

$$= \left(-x_{m-1}2^{m-1} + \sum_{i=0}^{m-2} x_{i}2^{i} Y_{v}\right) \left(-y_{n-1}2^{n-1} + \sum_{j=0}^{n-2} y_{j}2^{j}\right)$$

$$= \left(x_{m-1}x_{n-1}2^{m+n-2} + \sum_{i=0}^{m-2} \sum_{j=0}^{n-2} x_{i}y_{j}2^{i+j}\right)$$

$$-\left(\sum_{j=0}^{n-2} x_{m-1}y_{j}2^{m-1+j} + \sum_{i=0}^{m-2} y_{n-1}x_{i}2^{n-1+i}\right)$$

(2.16)

The above equation has partial products needed to be added and subtracted. The partial products with negative signs must be two's complemented to perform the addition instead of subtraction. Assuming the magnitude of a two's complement number Z is  $Z_v$ . Value of the negation of the two's complement number  $Z = (z_{k-1}, \dots, z_0)$  is as follows:

$$-Z_{v} = 2's complement of Z$$

$$= 1's complement of Z + 1$$

$$= -\overline{z_{k-1}}2^{k-1} + \sum_{i=0}^{k-2} \overline{z_{i}}2^{i} + 1$$

(2.17)

Therefore, the subtraction terms in the product equation,

$$2^{m-1} \left( -0 \cdot 2^n + 0 \cdot 2^{n-1} + \sum_{j=0}^{n-2} y_j x_{m-1} 2^j \right)$$

(2.18)

and

$$2^{n-1} \left( -0 \cdot 2^m + 0 \cdot 2^{m-1} + \sum_{i=0}^{m-2} y_{n-1} x_i 2^i \right)$$

(2.19)

are replaced with

$$2^{m-1} \left( -1 \cdot 2^n + 1 \cdot 2^{n-1} + \left( \sum_{j=0}^{n-2} \overline{y_j x_{m-1}} 2^j \right) + 1 \right)$$

(2.20)

and

$$2^{n-1}\left(-1\cdot 2^m + 1\cdot 2^{m-1} + \left(\sum_{i=0}^{m-2} \overline{y_{n-1}x_i}2^i\right) + 1\right)$$

(2.21)

respectively. Thus, the last two partial product rows, shown in Figure 11,

which need to be subtracted,

0 0

$$y_{n-1}x_{m-2} y_{n-1}x_{m-3} \cdots y_{n-1}x_0$$

(2.22)

and

0 0

$$y_{n-2}x_{m-1} y_{n-3}x_{m-1} \cdots y_0x_{m-1}$$

(2.23)

are replaced by

1 1

$$\overline{y_{n-1}x_{m-2}} \overline{y_{n-1}x_{m-3}} \cdots \overline{y_{n-1}x_0}$$

(2.24)

and

1 1

$$\overline{y_{n-2}x_{m-1}} \overline{y_{n-3}x_{m-1}} \cdots \overline{y_0x_{m-1}}$$

(2.25)

respectively. The additional "1"s are added to the  $p_{m-1}$  column and  $p_{n-1}$  column. And, the non-uniformity occurred in the last two rows due to the need for using NAND instead of AND to form the partial product bits can be avoided by using the following equivalences (2.26) and (2.27),

$$\begin{cases} 0, & for \ y_{n-1} = 0 \\ 2^{n-1} \left( -2^m + 2^{m-1} + \left( \sum_{i=0}^{m-2} \overline{x_i} 2^i \right) + 1 \right), & for \ y_{n-1} = 1 \end{cases}$$

(2.26)

and

$$\begin{cases} 0, & for \ x_{m-1} = 0 \\ 2^{m-1} \left( -2^n + 2^{n-1} + \left( \sum_{j=0}^{n-2} \overline{y_j} 2^j \right) + 1 \right), & for \ x_{m-1} = 1 \end{cases}$$

(2.27)

Following the equivalences (2.26) and (2.27), the above equations (2.20) and (2.21)can be rewritten as follows:

$$2^{n-1} \left( -2^m + 2^{m-1} + \overline{y_{n-1}} 2^{m-1} + y_{n-1} + \left( \sum_{i=0}^{m-2} y_{n-1} \overline{x_i} 2^i \right) \right)$$

(2.28)

and

$$2^{m-1} \left( -2^n + 2^{n-1} + \overline{x_{m-1}} 2^{n-1} + x_{m-1} + \left( \sum_{j=0}^{n-2} x_{m-1} \overline{y_j} 2^j \right) \right)$$

(2.29)

A simplified proof for Baugh-Wooley two's complement parallel array multiplier is presented in [33]. After achieving the uniformity at the last two rows and adding the constant terms, the rewritten partial product array with complete uniformity is shown in Figure 12.

A new high speed digital multiplier using modified pairwise and parallel addition algorithms is presented in [34] to improve the speed and the simulation results show that the speed and delay performance is two folds better than the conventional linear array multipliers. The delay and power consumption for this design is significantly better than the designed and optimized Baugh-Wooley multiplier.

#### 2.2.5 Vedic Multiplier

Vedic multiplier, which is based on Urdhva – Tiryakbhyam (UT) (vertical and crosswise) formulae, with fast adders (carry save adder, Brenk-Kung adder, and carry select adder) and by deploying compressors in place of full-adders and half adders to

minimize the power-delay-product (PDP) is proposed in [35]. Multipliers with operand width of 8-bit and 16-bit are designed, synthesized, and made proper comparisons with the synthesis results obtained from designing and synthesizing Ripple carry based Vedic multiplier (RCVM) [36], Carry Save array multiplier (CSAM) [37], compressor-based Vedic multiplier (CVM) [38], and modified Booth encoded Wallace tree multiplier (MBWM) [39]. Results comparison clearly shows that optimized Vedic multiplier presented shows significant improvement in delay and PDP with the area and power tradeoff. Another optimized Vedic multiplier with adaptable Manchester carry chain (MCC) adder, implemented with adaptable clocking scheme to be suitable to extend the use towards wider multipliers, for low power-delay product is presented in [40].

# 3 Optimization of radix-4 8 x 8 Booth multiplier

The discussion in the following chapter is substantially drawn from [41] [42] [43] where we first reported the development and evaluation of this technique.

#### 3.1 Introduction

The main motivation for optimization came from the observations made while designing the conventional Booth multiplier. Conventional Booth multiplier architecture is impressive for reducing the number of partial products to half, but the implementation needs further optimization to achieve low-cost and high-performance modified signed multiplier with Booth encoding. The improvements presented in [42] for an 8 x 8 Booth multiplier dealt with the unnecessary usage of full width adder and multiplier hardware, optimization of B2C, removal of adder in the first stage, and replacing the two-input encoder with three input encoders in the first stage. More details about the work in [42] are discussed in the sub-section 1.1 of this document. Further optimized 8 x 8 Booth multiplier is presented in [41] by majorly focusing on two aspects, (1) improving the speed by the execution of square root carry select adders with carry look ahead block in parallel to reduce the number of stages of addition, and (2) optimization of Booth encoder along with the B2C with bubble pushing and deploying a simple hardware by the fusion of the encoder logic and the multiplexer logic at every stage. Complete discussion about the implementation and results are included in the section 3.3 of this document.

## 3.2 Low power-delay-product radix-4 8 x 8 Booth multiplier [42]

Booth encoding scheme applied at each stage of the conventional Booth multiplier architecture shown in Figure 13(a) uses one of the five distinct operations, to result in a partial product in the respective stage. The five distinct operations include: (1) all 0's, (2) direct use of multiplicand, X, (3) multiplicand left shifted by one bit position, 2X, (4) two's complement of X, and (5) right shift the two's complemented X by one bit position, -2X. Except the two's complement operation to generate the -X as partial product at the respective stage, all other operations involve trivial and fast parallel computation of shift.

Design shown in Figure 13(a) avoid two's complement operation by deploying the adder-subtractor and switching the addition and subtraction operation relying on the MSB bit of the 3-bit group. But, it takes an additional hardware and power consumption due to the deployment of the number of XOR's at one of the multibit inputs of the adder at every stage. This leads to a significant power and area over head. Left shift operations are performed by hardwiring the input connections to the multi-bit 3-to-1 multiplexer to avoid the actual physical hardware. Moving forward to the next stage, which takes an adjacent group of 3-bits of multiplier to perform the encoding scheme, the possible partial product output is formed from one of the above mentioned five distinct values which are left shifted by two-bit positions because of the two-bit left shift to form 3-bit group. Hence, there is no need to generate the five possible values in any other stage but to be selected using the multiplexers at each stage while hardwiring the inputs to eliminate the inclusion of the left shift block. The optimized 8 x 8 Booth multiplier is proposed and presented in [43] [42], shown in Figure 13(b), minimized the encoder in the first stage from a 3-bit encoder to 2-bit encoder based on the fact that the LSB bit,  $y_{-1}$ , of the 3-bit group is always '0', the first stage adder-subtractor block is replaced with an optimized B2C, and the sizes of the 15-bit adder-subtractor blocks at each stage are reduced to 9-bit for eliminating the unnecessary computational cost at the LSB bits and sign bits at the MSB side. Optimized B2C presented in [42] is represented using equation (3.1) assuming the total number of bits of the word to be 2's complemented are odd where n is even and  $[a_n \ a_{n-1} \ \dots \ a_2 \ a_1 \ a_0]$  as input vector and  $[ac_n \ ac_{n-1} \ \dots \ a_2 \ a_1 \ a_0]$  as the two's complemented output

$$ac_0 = a_0$$

$$ac_1 = \overline{a_0} \oplus \overline{a_1}$$

$$ac_2 = \overline{a_2} \oplus (\overline{a_1} \cdot \overline{a_0}) = a_2 \oplus \overline{(\overline{a_1} \cdot \overline{a_0})}$$

$$ac_3 = \overline{a_3} \oplus (\overline{a_2} \cdot \overline{a_1} \cdot \overline{a_0}) = a_3 \oplus \overline{\left(a_2 + \overline{(\overline{a_1} \cdot \overline{a_0})}\right)}$$

...

$$ac_{n-1} = \overline{a_{n-1}} \oplus \overline{\left(a_{n-2} + \overline{\left(\overline{a_{n-3}} \cdot \overline{\left(a_{n-4} + \overline{\left(\overline{a_{n-5}} \cdot \cdots + \overline{\left(\overline{a_1} \cdot \overline{a_0}\right)}\right)}\right)}\right)}\right)}$$

$$ac_n = a_n \oplus \overline{\left(\overline{a_{n-2}} \cdot \overline{\left(\overline{a_{n-3}} + \overline{\left(\overline{a_{n-4}} \cdot \overline{\left(\overline{a_{n-5}} + \cdots + \overline{\left(\overline{a_1} \cdot \overline{a_0}\right)}\right)}\right)}\right)}\right)}$$

(3.1)

## 3.3 Low-cost and high-performance radix-4 8 x 8 Booth multiplier [41]

Booth multiplier architecture is further optimized in [41], shown in Figure 14, by implementing the following strategies: (1) replacing the adder-subtractor blocks in all stages with only adders and using the B2C output to feed the -X and -2X inputs to generate the partial products in all stages where necessary to reduce the power consumption and design area, (2) sequential addition of partial products is replaced with parallel addition, number of stages of addition are reduced to two, to improve the speed while keeping the area of partial product reduction hardware almost same, (3) encoded partial products are generated directly using the speed optimized encoder block with

inherent multiplexer logic, (4) B2C block in the worst delay path is further optimized to reduce the power consumption and design area, and (5) Square root carry select adders with carry look ahead blocks are used to improve the speed performance with a power and area tradeoff.

The anatomy of the radix-4 8 x 8 signed Booth multiplier with parallel adders is presented in [41] is illustrated in Figure 15. This parallel addition with careful grouping has higher performance advantage compared to employing the series addition of the partial products in [42] [43] [44] [45] [46]. The worst delay path includes B2C, Booth encoder, 10-bit SQCS with CLA, and 11-bit SQCS with CLA. Hence, all the blocks in worst delay path are optimized for speed. The explanation about each sub-optimization

strategy used is included in the following sub-sections. Layout of the modified 8x8 Booth multiplier with parallel encoding scheme and parallel partial product reduction, which is synthesized at 500 MHz clock frequency and performed PnR, using Synopsys Design Compiler (DC) and IC compiler (ICC) respectively, is shown in Figure 16. Total chip area of the layout shown in the following figure is 2058.566 ( $\mu$ m)<sup>2</sup> with the standard cell utilization factor of 57.32%. Hence, the total cell area is nearly 1180 ( $\mu$ m)<sup>2</sup> with total number of standard cells used are 358.

Figure 16 Layout of the modified Radix-4 8x8 signed Booth multiplier with parallel encoding and additions [41]

#### 3.3.1 Booth encoder optimization & partial product generation

Pre-computation stage first encoder for the first partial product, PP1, generation is reduced to a two-input encoder, 4 to 1 multiplexer, since the LSB bit,  $y_{-1}$ , is always '0' and can be ignored. The rest of the encoding uses  $y_1$  and  $y_0$  bits of the multiplicand to generate the partial products based on the encoding scheme shown in Table 3.1. The operation of choosing one of the four possible partial products is performed using a 9-bit wide 4 to 1 multiplexer, shown in Figure 17. The multiplexer takes four inputs, 0, X, -X, and -2X, with two LSB bits of the multiplier as selection inputs. The negative value of the multiplicand, -X, is generated by using the B2C and by feeding -2X, output from B2C, as an input after arithmetic left shift is performed just by hardwiring while avoiding the actual physical hardware. Discussion about the optimized B2C is included in a later subsection.

Table 3.1 First stage encoding scheme [41]

| ${\cal Y}_0$ | $\mathcal{Y}_{-1}$ | Partial Product |

|--------------|--------------------|-----------------|

| 0            | 0                  | 0               |

| 1            | 0                  | +X              |

| 0            | 0                  | -2X             |

| 1            | 0                  | -X              |

|              | 0<br>1<br>0<br>1   | 0 0 0 1         |

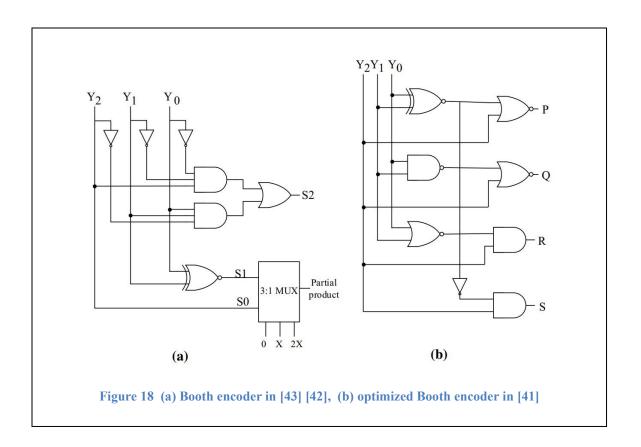

The three encoders needed for the generation of the next three partial products, PP2, PP3, and PP4, in the pre-computation stage run in parallel, shown in Figure 15, and are built on a same logic. The optimized encoder logic presented in [41], achieved by applying bubble pushing and Boolean logic minimization techniques, is shown in Figure 18 (b), and is compared to the encoder presented in [43] [42]. Typical Booth encoder takes in three input bits and yields three selection output bits, S2, S1, and S0, at each stage to fed to the multiplexer to choose one of the eight possible values based on the booth encoder strategy. Where in the optimized encoder results in four output bits, P, Q, R, and S, to choose between {X, 2X, -X, -2X} without the need for an exclusive multiplexer since the simplified multiplexer functionality is fused with the encoder to generate the partial products with reduced delay and reduced utilization of the design space. The Boolean logic used to generate the P, Q, R, and S scalars is shown in the Figure 18 (b) and the Boolean equation representation of the scalars as follows:

$$P = \overline{(y_0 \ominus y_1) + y_2}$$

(3.2)

$$Q = \overline{(y_0 \cdot y_1)} + y_2$$

$$S = (y_0 \oplus y_1) \cdot y_2 \tag{3.5}$$

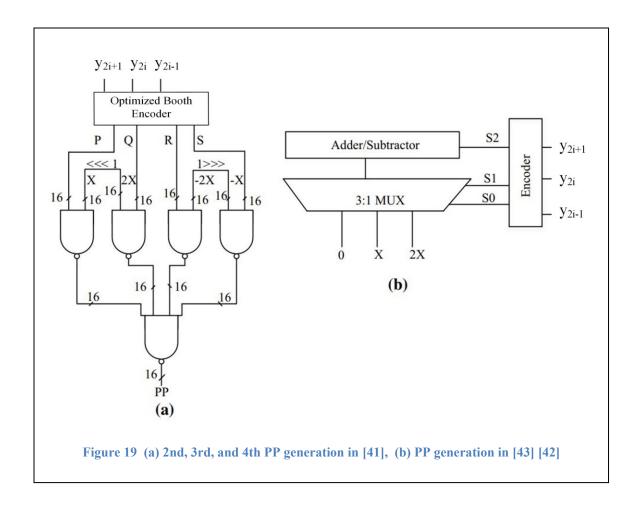

The fused encoder and multiplexer logic presented in [41] for the generation of the 2<sup>nd</sup>, 3<sup>rd</sup>, and 4<sup>th</sup> partial products is shown in Figure 19 (a) and is compared with the conventional Booth encoder and the multiplexer, shown in Figure 19 (b), used to generate

$R = \overline{(y_0 + y_1)} \cdot y_2$

the partial products at each stage. P, Q, R, and S scalar outputs from the optimized encoder are used to select the X, 2X, -2X, and -X vectors respectively to generate the partial product, PP, and the Boolean representation of the selection hardware is represented using the following equation (3.6):

$$PP = (P \cdot X) + (Q \cdot 2X) + (R \cdot (-2X)) + (S \cdot (-X))$$

$$= \overline{(P \cdot X) \cdot \overline{(Q \cdot 2X)} \cdot \overline{(R \cdot (-2X))} \cdot \overline{(S \cdot (-X))}}$$

(3.6)

Selection inputs P, Q, R, and S are enabled with the 3-bit input vectors {001, 010}, {011}, {100}, and {101, 110} respectively. In case of the input vectors '000' and '111', all the output bits of the encoder are 0's and hence the fifth possible partial product of all 0's is assigned to the PP output vector.

## 3.3.2 Reduction of Partial Products using Two-Stage Parallel Addition

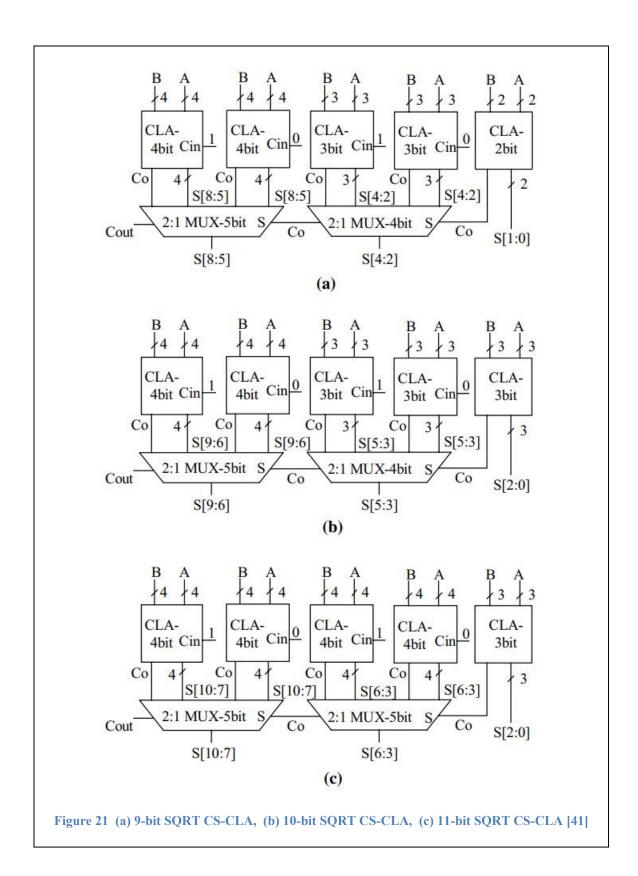

As mentioned above, the three partial products generated are summed to have the final product. Square root (SQRT) carry select adder with carry look ahead (CSA-CLA) blocks are used to increase the computation speed with the power and area trade-off. Carry select blocks works on a simple and very effective way to increase the speed by precomputing the possible sum outputs with the assumption of '0' carry-in and '1' carry-in. By the time of actual carry-in signal arrival at a particular block, two possible sum values are ready to be selected in parallel by the multiplexer. Including CLA logic in sub-block further improves the speed performance by the very quick carry out generation based on the multi-bit propagate and generate chain. The parallel addition structure is

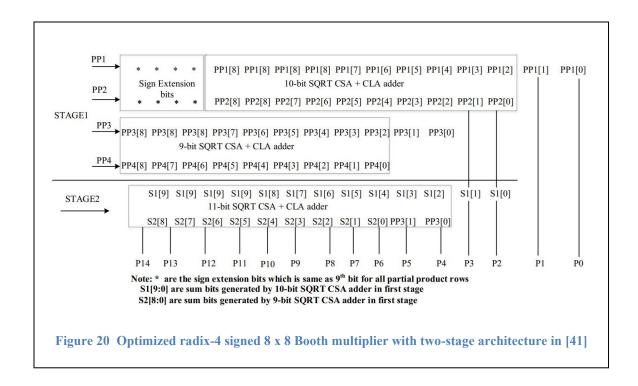

carefully designed following the grouping of the partial products illustrated in Figure 20. All the partial products, PP1, PP2, PP3, and PP4, generated are of 9-bit wide, PP[9:0], hence a 9-bit B2C is enough instead of a full width, 15-bit, B2C. PP1[8], PP2[8], and PP3[8] are repeated as extension bits for keeping the sign of the partial product. PP1[0] and PP1[1] are the final product bits P[0] and P[1] respectively. 10-bit SQRT CS-CLA with 3-bit CLA, 3-bit CS-CLA, and 4-bit CS-CLA sub-blocks, shown in Figure 21 (b), is used to sum the partial products PP1[11:2] and PP2[9:0], where PP1[11:9] are the sign extension bits formed by repeating the sign indicator bit, PP1[8]. A 9-bit SQRT CS-CLA with 2-bit CLA, 3-bit CS-CLA, and 4-bit CS-CLA sub-blocks, shown in Figure 21 (a), is used to sum the partial products PP3[10:2] and PP4[8:0], where PP3[10:9] are the sign extension bits formed by repeating the sign bit, PP3[8]. At each partial product row to be summed in stage 1, the (n+1)<sup>th</sup> bit indicates the sign of that partial products and that bit value is copied across the proceeding MSB bits until reaching the bit index of 14, with the indexing begin at 0, with reference to the indices of the final product bits. Like the 10-bit adder, 9-bit adder takes the first partial product with a starting index of 2. The remaining LSB bits of the first input vector PP3, PP3[0] and PP[1], are carried down to the second stage addition to fill in the gap to form a rectangular group structure for forming a SQRT CS-CLA. These two adders, 9-bit adder and 10-bit adder, run in parallel for the stage 1 reduction resulting in two intermittent output vectors, S1 and S2, to be further reduced, summed, in the final stage, stage 2.

The two sum outputs, S1[12:2] and S2[8:0], along with the two partial product bits, PP3[1:0], left unprocessed, from stage 1 are fed to the 11-bit SQRT CS-CLA in the final stage, stage 2. As shown in Figure 21 (c), 11-bit SQRT CS-CLA constitutes a 3-bit CLA block, 4-bit CS-CLA block, and 4-bit CS-CLA block. This parallel addition with two stage structure is reducing the two adder delays compared with the designs presented in [44] [45] [46], and reducing one adder delay if compared to the design in [42].

#### 3.3.3 B2C optimization

Binary two's complement block is one of the important blocks needed to be optimized for the reduction in delay since it has the ripple structure. An optimized B2C is presented in [42], discussion is included in the sub-section 1.1, shown in Figure 22 (a), and the design is better optimized in [41], shown in Figure 22 (b), for the reduction of area and power consumption. Based on the widely accepted and observed fact that the inverters at the inputs consume more power due to high switching activity, reduction of area and power consumption is achieved by bubble pushing the inverters at the inputs used in [42]. The Boolean equations for the 9-bit B2C used in [42] and [41], shown in Figure 22, are as follows, where  $[a_n \ a_{n-1} \ \dots \ a_2 \ a_1 \ a_0]$  as input vector and  $[ac_n \ ac_{n-1} \ \dots \ a_2 \ a_1 \ a_0]$  as the two's complemented output:

$$ac_{0} = a_{0}$$

$$ac_{1} = a_{0} \oplus a_{1}$$

$$ac_{2} = \overline{a_{0} + a_{1}} \ominus a_{2}$$

$$ac_{3} = \overline{a_{0} + a_{1} + a_{2}} \ominus a_{3}$$

$$ac_{4} = \overline{a_{0} + a_{1} + a_{2} + a_{3}} \ominus a_{4}$$

$$ac_{5} = \overline{((a_{0} + a_{1} + a_{2} + a_{3}) + a_{4})} \ominus a_{5}$$

$$= \overline{\overline{a_{0} + a_{1} + a_{2} + a_{3}} + a_{4}} \ominus a_{5}$$

$$ac_{6} = \overline{((a_{0} + a_{1} + a_{2} + a_{3}) + a_{4} + a_{5})} \ominus a_{6}$$

$$= \overline{\overline{a_{0} + a_{1} + a_{2} + a_{3}}} + a_{4} + a_{5} \ominus a_{6}$$

$$ac_{7} = \overline{((a_{0} + a_{1} + a_{2} + a_{3}) + a_{4} + a_{5} + a_{6})} \ominus a_{7}$$

$$= \overline{\overline{a_{0} + a_{1} + a_{2} + a_{3}}} + a_{4} + a_{5} + a_{6} \ominus a_{7}$$

$$ac_{8} = \overline{((a_{0} + a_{1} + a_{2} + a_{3}) + a_{4} + a_{5} + a_{6} + a_{7}) \oplus a_{8}}$$

$$= (a_{0} + a_{1} + a_{2} + a_{3} + a_{4} + a_{5} + a_{6} + a_{7}) \oplus a_{8}$$

$$= \overline{a_{0} + a_{1} + a_{2} + a_{3}} + a_{4} + a_{5} + a_{6} + a_{7} \oplus a_{8}$$

$$(3.7)$$

$a_0$  $a_4$  $a_8$  $ac_0$  $ac_4$ ac<sub>5</sub> ac<sub>7</sub> ac<sub>3</sub> (a)  $a_0$  $a_2$  $a_3$  $a_4$  $a_5$  $a_6$  $a_7$  $a_8$  $ac_0 ac_1$  $ac_4$ (b) Figure 22. (a) optimized B2C using bubble pushing in [42], (b) better optimized B2C in [41]

The synthesis results for the two B2C designs are compared in the following Table 3.2. Synthesis is performed on the two designs designed in Synopsys 32nm CMOS RVT standard cells at 500 MHz frequency and 1.05 supply voltage with the help of

Synopsys design compiler (DC). Reduction in design area and power consumption can be observed with a very small delay trade-off.

Table 3.2 Comparison of the synthesis (pre-layout) results for the B2C designs [41]

| B2C Design          | Frequency | Area        | Power | Delay |

|---------------------|-----------|-------------|-------|-------|

|                     | (MHz)     | $(\mu m)^2$ | (µW)  | (ns)  |

| Boppana et al. [41] | 500       | 56.41       | 15.15 | 0.41  |

| B2C in [42]         | 500       | 63.02       | 16.85 | 0.4   |

# 4 Proposed Multiplier Architecture based on radix-8 (3-bit grouping) structure

Modified booth multiplier's encoding scheme with the deployment of the parallel adders of square root carry select (SQCS) structure, constitutes carry look ahead (CLA) sub-blocks, is presented in [41], and has achieved a significant increase in speed by reducing the worst path delay and a significant decrease in the power consumption with a small reduction in area. As shown in Table 4.1, Booth encoding reduces the number of partial products by half, and the parallel execution of the adders in a binary tree style requires the same number of adders required by the series execution of the adders in summing the partial products while the number of stages required to sum the partial products to compute the final product are reduced to  $\log_2 N$  from  $\frac{N}{2} - 1$ .

Table 4.1 Booth multiplier with binary tree style reduction of partial products using adders

| Multiplier | No. of    | No. of additions | Complexity in                       | Complexity in Time     |

|------------|-----------|------------------|-------------------------------------|------------------------|

| size (N)   | PPs (N/2) | (N/2-1)          | Hardware (#Adders)                  | (PP reduction time)    |

| 8          | 4         | 2+1=3            | $O(N) = \frac{N}{2} - 1$            | $O(\log N) = \log_2 N$ |

| 16         | 8         | 4+2+1=7          | $O(N) = \frac{N}{2} - 1$            | $O(\log N) = \log_2 N$ |

| 32         | 16        | 8+4+2+1=15       | $O(N) = \frac{N}{2} - 1$            | $O(\log N) = \log_2 N$ |

| 64         | 32        | 16+8+4+2+1=31    | $O(N) = \frac{\overline{N}}{2} - 1$ | $O(\log N) = \log_2 N$ |

Though the state-of-the-art modified Booth multiplier architectures use the radix-8 Booth encoding with 3-bit grouping of the multiplier bits, the effective number of multiplier bits, from LSB to MSB, used in partial product generation at any stage are two.

Hence, the Booth multiplier architecture can be called as a radix-4 structure instead of radix-8 structure. The proposed architecture in this work is an attempt to prove that the use of the higher radix, radix-8 in this work, by deploying a non-trivial block, which further reduces the number of partial products to be added compared to the Booth architectures, and area-power-delay aware grouping of the partial products results in achieving a significant advantage, especially for the larger word size multipliers such as 32-bit, 64-bit, etc. The proposed structure first converts the multiplicand and multiplier to its magnitudes, pre-compute the non-trivial functions, NT1, NT2, and NT3, included in Table 4.2 which depicts the separation of the eight functions to four trivial and four non-trivial functions.

Table 4.2 Proposed radix-8 (3-bit) grouping to separate trivial and non-trivial computations

| Trivial                 |                             |                 |  |  |

|-------------------------|-----------------------------|-----------------|--|--|

| 0 (000)                 | By-pass                     | N0 (No-Op)      |  |  |

| 1 (001)                 | << 0 (No shift or addition) | T0              |  |  |

| 2 (010)                 | << 1 (Left shift by 1)      | T1              |  |  |

| 4 (100)                 | << 2 (Left shift by 2)      | T2              |  |  |

| Non-Trivial Non-Trivial |                             |                 |  |  |

| 3 (011)                 | 2x+1x (or) $4x-1x$          | NT1             |  |  |

| 5 (101)                 | 4x+1x                       | NT2             |  |  |

| 6 (110)                 | 4x+2x                       | S1 = (NT1) << 1 |  |  |

| 7 (111)                 | 8x-x (or) 4x+2x+1x          | NT3             |  |  |

### 4.1 8 x 8 signed multiplication using the proposed design :

As seen in Table 4.2, All the trivial functions involve one of the four operations: no operation, all 0's; the magnitude of the multiplicand (X) with no shift, X; X left shifted by 1 bit position, 2X; X left shifted by 2-bit positions, 4X. The complete working of the proposed radix-8 with the grouping of 3-bit multiplier bits for the 8x8 signed multiplier is clearly illustrated using the example-1 and example-2 shown in Figure 23

and Figure 24 respectively. As a first step, the magnitudes of the multiplicand, A, and multiplier, B, are computed as  $A_p$  and  $B_p$ . Magnitude of the negative number is computed using the 2's complement and the magnitude of the positive number is the number itself. In example 1, the negative multiplicand, A = -72 (1011 1000), is converted to its 2's complement, Ap (0100 1000), which is denoted as X for the ease of representation in later steps. Taking the X as an input, the three non-trivial computations, 3X, 5X, and 7X, are computed by performing the addition operations. 3X is formed by summing the X and 2X, 5X is formed by summing the X and 4X, and 7X is formed using the summation of -X and 8X instead of summing X, 2X, and 4X to complete reduce the number of additions.

The first 6-bits of  $B_p$  on the LSB side are grouped into two 3-bit groups and the first two partial products in stage 1 are calculated following the computation criteria provided in Table 4.2. Indexing always starts from the LSB side with 0 as start index.

The second partial product needs to be shifted by three bits since the second group multiplier bits start from index 3. The bit, '1', at position 7 of index 6 from the LSB side forms the third partial product of X left shifted by 6-bit positions. If this lone bit is '0', then the third partial product contains all 0's. The first two partial products enclosed in the L-shaped box are added together and the third partial product is carried to the next stage to perform the addition in stage 2. In two stages the magnitude of the product is computed as 001011100010000. As a final post computation step, the sign of the result should be decided based on the combination of signs of the original inputs, A and B. If the signs of A and B are opposite,  $A[7] \oplus B[7] == 1$ , and the magnitude of multiplier is not the max value of 128,  $\sim B_p[7] == 1$ , then the final magnitude obtained is 2's complement. XOR operation is represented as ^ and NOT operation is represented as ! in all the figures with example illustrations. The sign bit of a multiplier or multiplicand stays same even after performing the 2's complement in only one case where the actual value is the lowest, -128, i.e., the magnitude value is at its maximum for the 8-bit signed number.

Like the example 1, example 2 also starts with the first of magnitude calculation of both multiplicand, A = 6 (0000 0110), and multiplier, B = -36 (1101 1100), 2's complement of B, Bp=(00100100) shown in Figure 24. As a next step, the non-trivial computation required are performed. In the proceeding step, the grouping of bits of the multiplier magnitude,  $B_p$ , is completed and the three partial products are generated based on the two 3-bit groups and the lone bit at index 6. Required additions are computed in stage 1 and stage 2. The result after performing the summation is the magnitude of the product. The sign of the product is determined based on the signs of the actual inputs. If

the signs of the actual inputs are opposite, then the result obtained from the summation at stage 2 is 2's complemented to find the actual value of the product.